FORCOM TECHNOLOGY CORPORATION

FT-1339L

|

Processor |

80486SX/AM486DX/80486DX/AM486DX2/AM486DX2(WB)/ AM486DX2(WT)/80486DX2/AM486DX4/AM486DX4(WB)/ AM486DX4(WT(/80486DX4/CXM7/STM7/IBMM7/TIM7/CX5X86(WB)/ CX5X86(WT)/ST5X86(WB)/ST5X86(WT)/IBM5X86(WB)/IBM5X86(WT)/ TI5X86(WB)/TI5X86(WT)/ AM5X86(WB)/AM5X86(WT) |

|

Processor Speed |

25/33/40/50(internal)/50/66(internal)/75(internal)/100(internal)MHz |

|

Chip Set |

SIS |

|

Video Chip Set |

Cirrus Logic |

|

Maximum Onboard Memory |

64MB (EDO supported) |

|

Maximum Video Memory |

2MB |

|

Cache |

128/256/512KB |

|

BIOS |

Award |

|

Dimensions |

220mm x 200mm |

|

I/O Options |

Floppy drive interface, green PC connector, IDE interfaces (2), parallel port, PS/2 mouse interface, serial ports (2), VGA feature connector, VGA port, riser slot, IR connector |

|

NPU Options |

None |

|

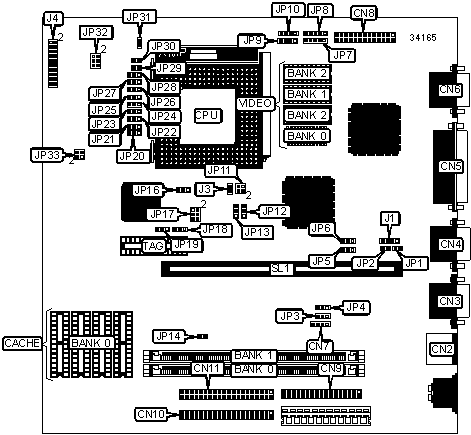

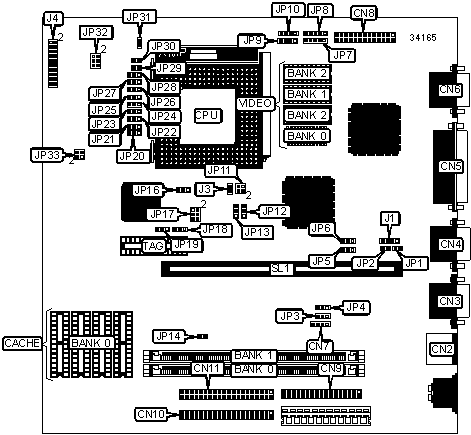

CONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

PS/2 mouse port |

CN2 |

External battery |

J1 |

|

Serial port 1 |

CN3 |

Green PC connector |

J3 |

|

Serial port 2 |

CN4 |

Speaker |

J4 pins 1/3/5/7 |

|

Parallel port |

CN5 |

Reset switch |

J4 pins 2 & 4 |

|

VGA port |

CN6 |

IDE interface LED |

J4 pins 6 & 8 |

|

IR connector |

CN7 |

Power LED & keylock |

J4 pins 11/13/15/17/19 |

|

VGA feature connector |

CN8 |

Turbo LED |

J4 pins 12 & 14 |

|

Floppy drive interface |

CN9 |

Turbo switch |

J4 pins 16/18/20 |

|

IDE interface 1 |

CN10 |

Riser slot |

SL1 |

|

IDE interface 2 |

CN11 | ||

|

USER CONFIGURABLE SETTINGS | |||

|

Function |

Label |

Position | |

|

» |

Factory configured - do not alter |

JP1 |

Unidentified |

|

» |

Factory configured - do not alter |

JP2 |

Unidentified |

|

» |

On board video enabled |

JP5 |

Pins 1 & 2 closed |

|

On board video disabled |

JP5 |

Pins 2 & 3 closed | |

|

» |

CMOS memory normal operation |

JP6 |

Pins 1 & 2 closed |

|

CMOS memory clear |

JP6 |

Pins 2 & 3 closed | |

|

» |

Factory configured - do not alter |

JP11 |

Unidentified |

|

» |

Factory configured - do not alter |

JP12 |

Unidentified |

|

Monitor type select color |

JP14 |

Closed | |

|

Monitor type select monochrome |

JP14 |

Open | |

|

» |

Power good signal detect from board |

JP20 |

Pins 2 & 3 closed |

|

Power good signal detect from power supply |

JP20 |

Pins 1 & 2 closed | |

|

Buzzer enabled |

JP31 |

Closed | |

|

» |

Buzzer disabled |

JP31 |

Open |

|

DRAM CONFIGURATION | ||

|

Size |

Bank 0 |

Bank 1 |

|

1MB |

(1) 256K x 36 |

None |

|

2MB |

(1) 512K x 36 |

None |

|

2MB |

(1) 256K x 36 |

(1) 256K x 36 |

|

3MB |

(1) 512K x 36 |

(1) 256K x 36 |

|

4MB |

(1) 1M x 36 |

None |

|

4MB |

(1) 512K x 36 |

(1) 512K x 36 |

|

DRAM CONFIGURATION (CON’T) | ||

|

Size |

Bank 0 |

Bank 1 |

|

5MB |

(1) 1M x 36 |

(1) 256K x 36 |

|

6MB |

(1) 1M x 36 |

(1) 512K x 36 |

|

8MB |

(1) 2M x 36 |

None |

|

8MB |

(1) 1M x 36 |

(1) 1M x 36 |

|

9MB |

(1) 2M x 36 |

(1) 256K x 36 |

|

10MB |

(1) 2M x 36 |

(1) 512K x 36 |

|

12MB |

(1) 2M x 36 |

(1) 1M x 36 |

|

16MB |

(1) 4M x 36 |

None |

|

16MB |

(1) 2M x 36 |

(1) 2M x 36 |

|

17MB |

(1) 4M x 36 |

(1) 256K x 36 |

|

18MB |

(1) 4M x 36 |

(1) 512K x 36 |

|

20MB |

(1) 4M x 36 |

(1) 1M x 36 |

|

24MB |

(1) 4M x 36 |

(1) 2M x 36 |

|

32MB |

(1) 8M x 36 |

None |

|

32MB |

(1) 4M x 36 |

(1) 4M x 36 |

|

33MB |

(1) 8M x 36 |

(1) 256K x 36 |

|

34MB |

(1) 8M x 36 |

(1) 512K x 36 |

|

36MB |

(1) 8M x 36 |

(1) 1M x 36 |

|

40MB |

(1) 8M x 36 |

(1) 2M x 36 |

|

48MB |

(1) 8M x 36 |

(1) 4M x 36 |

|

64MB |

(1) 8M x 36 |

(1) 8M x 36 |

|

Note: Board accepts EDO memory. Banks are interchangeable. | ||

|

CACHE CONFIGURATION | ||

|

Size |

Bank 0 |

TAG |

|

128KB |

(4) 32K x 8 |

(1) 8K x 8 |

|

256KB |

(4) 64K x 8 |

(1) 32K x 8 |

|

512KB |

(4) 128K x 8 |

(1) 32K x 8 |

|

CACHE JUMPER CONFIGURATION | ||

|

Size |

JP18 |

JP19 |

|

128KB |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

|

256KB |

Pins 1 & 2 closed |

Pins 2 & 3 closed |

|

512KB |

Pins 2 & 3 closed |

Pins 2 & 3 closed |

|

VIDEO MEMORY CONFIGURATION | |||

|

Size |

Bank 0 |

Bank 1 |

Bank 2 |

|

512KB |

512MB |

None |

None |

|

1MB |

512MB |

512MB |

None |

|

2MB |

512MB |

512MB |

1MB |

|

CPU SPEED SELECTION | ||

|

Speed |

JP13 |

JP17 |

|

25MHz |

Pins 1 & 2 closed |

Open |

|

33MHz |

Pins 1 & 2 closed |

Pins 1 & 2, 3 & 4 closed |

|

40MHz |

Pins 2 & 3 closed |

Pins 1 & 2 closed |

|

50iMHz |

Pins 1 & 2 closed |

Open |

|

50MHz |

Pins 2 & 3 closed |

Pins 3 & 4 closed |

|

66iMHz |

Pins 1 & 2 closed |

Pins 1 & 2, 3 & 4 closed |

|

75iMHz |

Pins 1 & 2 closed |

Open |

|

100iMHz |

Pins 1 & 2 closed |

Pins 1 & 2, 3 & 4 closed |

|

CPU TYPE SELECTION | |||||

|

Type |

JP7 |

JP8 |

JP9 |

JP10 |

JP16 |

|

80486SX |

4 & 5 |

Open |

2 & 3 |

Open |

1 & 2 |

|

AM486DX |

4 & 5 |

Open |

1 & 2, 3 & 4 |

Open |

1 & 2 |

|

80486DX |

4 & 5 |

Open |

1 & 2, 3 & 4 |

Open |

1 & 2 |

|

AM486DX2 |

4 & 5 |

Open |

1 & 2, 3 & 4 |

Open |

1 & 2 |

|

AM486DX2 (V8B, WB, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX2 (V8B, WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX2 (V8B, WT, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX2 (V8B, WT, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX2 (V8T) |

4 & 5 |

Open |

1 & 2, 3 & 4 |

Open |

1 & 2 |

|

80486DX2 |

4 & 5 |

Open |

1 & 2, 3 & 4 |

Open |

1 & 2 |

|

AM486DX4 (V8B, WB, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX4 (V8B, WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX4 (V8B, WT, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX4 (V8B, WT, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM486DX4 (V8T) |

4 & 5 |

Open |

1 & 2, 3 & 4 |

Open |

1 & 2 |

|

80486DX4 (2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

3 & 4 |

1 & 2 |

|

80486DX4 (2.5x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

3 & 4 |

1 & 2 |

|

80486DX4 (3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

3 & 4 |

1 & 2 |

|

CX M7 |

4 & 5 |

2 & 3 |

1 & 2, 3 & 4 |

2 & 3 |

1 & 2 |

|

ST M7 |

4 & 5 |

2 & 3 |

1 & 2, 3 & 4 |

2 & 3 |

1 & 2 |

|

IBM M7 |

4 & 5 |

2 & 3 |

1 & 2, 3 & 4 |

2 & 3 |

1 & 2 |

|

TI M7 |

4 & 5 |

2 & 3 |

1 & 2, 3 & 4 |

2 & 3 |

1 & 2 |

|

CX 5X86 (WB, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

CX 5X86 (WT, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

CX 5X86 (WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

CX 5X86 (WT, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

ST 5X86 (WB, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

ST 5X86 (WT, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

CPU TYPE SELECTION (CON’T) | |||||

|

Type |

JP7 |

JP8 |

JP9 |

JP10 |

JP16 |

|

ST 5X86 (WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

ST 5X86 (WT, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

IBM 5X86 (WB, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

IBM 5X86 (WT, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

IBM 5X86 (WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

IBM 5X86 (WT, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

TI 5X86 (WB, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

TI 5X86 (WT, 2x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

TI 5X86 (WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

TI 5X86 (WT, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM 5X86 (WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM 5X86 (WT, 4x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM 5X86 (WB, 3x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

AM 5X86 (WT, 4x) |

4 & 5 |

4 & 5 |

1 & 2, 3 & 4 |

1 & 2, 3 & 4 |

1 & 2 |

|

Note: Pins designated should be in the closed position. | |||||

|

CPU TYPE SELECTION (CON’T) | |||||

|

Type |

JP21 |

JP22 |

JP23 |

JP24 |

JP25 |

|

80486SX |

Open |

Open |

Open |

Open |

Open |

|

AM486DX |

Open |

Open |

Open |

Open |

2 & 3 |

|

80486DX |

Open |

Open |

Open |

Open |

2 & 3 |

|

AM486DX2 |

Open |

Open |

Open |

Open |

2 & 3 |

|

AM486DX2 (V8B, WB, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

AM486DX2 (V8B, WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM486DX2 (V8B, WT, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

AM486DX2 (V8B, WT, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM486DX2 (V8T) |

Open |

Open |

Open |

Open |

2 & 3 |

|

80486DX2 |

Open |

Open |

Open |

Open |

2 & 3 |

|

AM486DX4 (V8B, WB, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

AM486DX4 (V8B, WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM486DX4 (V8B, WT, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

AM486DX4 (V8B, WT, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM486DX4 (V8T) |

Open |

Open |

Open |

Open |

2 & 3 |

|

80486DX4 (2x) |

Open |

Open |

2 & 3 |

Open |

2 & 3 |

|

80486DX4 (2.5x) |

Open |

Open |

1 & 2 |

Open |

2 & 3 |

|

80486DX4 (3x) |

Open |

Open |

Open |

Open |

2 & 3 |

|

CX M7 |

2 & 3 |

2 & 3 |

Open |

Open |

2 & 3 |

|

ST M7 |

2 & 3 |

2 & 3 |

Open |

Open |

2 & 3 |

|

IBM M7 |

2 & 3 |

2 & 3 |

Open |

Open |

2 & 3 |

|

CPU TYPE SELECTION (CON’T) | |||||

|

Type |

JP21 |

JP22 |

JP23 |

JP24 |

JP25 |

|

TI M7 |

2 & 3 |

2 & 3 |

Open |

Open |

2 & 3 |

|

CX 5X86 (WB, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

CX 5X86 (WT, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

CX 5X86 (WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

CX 5X86 (WT, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

ST 5X86 (WB, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

ST 5X86 (WT, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

ST 5X86 (WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

ST 5X86 (WT, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

IBM 5X86 (WB, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

IBM 5X86 (WT, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

IBM 5X86 (WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

IBM 5X86 (WT, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

TI 5X86 (WB, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

TI 5X86 (WT, 2x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

TI 5X86 (WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

TI 5X86 (WT, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM 5X86 (WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM 5X86 (WT, 4x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

AM 5X86 (WB, 3x) |

1 & 2 |

Open |

Open |

2 & 3 |

2 & 3 |

|

AM 5X86 (WT, 4x) |

1 & 2 |

Open |

2 & 3 |

2 & 3 |

2 & 3 |

|

Note: Pins designated should be in the closed position. | |||||

|

CPU TYPE SELECTION (CON’T) | |||||

|

Type |

JP26 |

JP27 |

JP28 |

JP29 |

JP30 |

|

80486SX |

Open |

Open |

Open |

Open |

Open |

|

AM486DX |

Open |

Open |

Open |

Open |

Open |

|

80486DX |

Open |

Open |

Open |

Open |

Open |

|

AM486DX2 |

Open |

Open |

Open |

Open |

Closed |

|

AM486DX2 (V8B, WB, 2x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

AM486DX2 (V8B, WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

AM486DX2 (V8B, WT, 2x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

AM486DX2 (V8B, WT, 3x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

AM486DX2 (V8T) |

Open |

Open |

Open |

Open |

Closed |

|

80486DX2 |

Open |

Open |

Open |

Open |

Open |

|

AM486DX4 (V8B, WB, 2x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

AM486DX4 (V8B, WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

AM486DX4 (V8B, WT, 2x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

AM486DX4 (V8B, WT, 3x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

CPU TYPE SELECTION (CON’T) | |||||

|

Type |

JP26 |

JP27 |

JP28 |

JP29 |

JP30 |

|

AM486DX4 (V8T) |

Open |

Open |

Open |

Open |

Closed |

|

80486DX4 (2x) |

2 & 3 |

Open |

Open |

Open |

Closed |

|

80486DX4 (2.5x) |

2 & 3 |

Open |

Open |

Open |

Closed |

|

80486DX4 (3x) |

2 & 3 |

Open |

Open |

Open |

Closed |

|

CX M7 |

1 & 2 |

Open |

Open |

Open |

Closed |

|

ST M7 |

1 & 2 |

Open |

Open |

Open |

Closed |

|

IBM M7 |

1 & 2 |

Open |

Open |

Open |

Closed |

|

TI M7 |

1 & 2 |

Open |

Open |

Open |

Closed |

|

CX 5X86 (WB, 2x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

CX 5X86 (WT, 2x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

CX 5X86 (WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

CX 5X86 (WT, 3x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

ST 5X86 (WB, 2x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

ST 5X86 (WT, 2x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

ST 5X86 (WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

ST 5X86 (WT, 3x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

IBM 5X86 (WB, 2x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

IBM 5X86 (WT, 2x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

IBM 5X86 (WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

IBM 5X86 (WT, 3x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

TI 5X86 (WB, 2x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

TI 5X86 (WT, 2x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

TI 5X86 (WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

TI 5X86 (WT, 3x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

AM 5X86 (WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

AM 5X86 (WT, 4x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

AM 5X86 (WB, 3x) |

2 & 3 |

Open |

1 & 2 |

Open |

Closed |

|

AM 5X86 (WT, 4x) |

2 & 3 |

Open |

2 & 3 |

Open |

Closed |

|

Note: Pins designated should be in the closed position. | |||||

|

CPU VOLTAGE SELECTION | ||

|

Voltage |

JP32 |

JP33 |

|

3.3v |

Pins 1 & 2 closed |

Pins 1 & 3, 2 & 4 closed |

|

3.45v |

Pins 3 & 4 closed |

Pins 1 & 3, 2 & 4 closed |

|

4v |

Pins 5 & 6 closed |

Pins 1 & 3, 2 & 4 closed |

|

5v |

N/A |

Pins 1 & 2, 3 & 4 closed |

|

IR SELECTION | ||

|

Setting |

JP3 |

JP4 |

|

U3 is 665IR, IR via CN7 |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

|

U3 uses 665GT/669 or 665IR without IR |

Pins 2 & 3 closed |

Pins 2 & 3 closed |