# SHARP SERVICE MANUAL

CODE: 00ZPC4741SM-E

## PERSONAL COMPUTER

PC-4741 PC-4721 MODEL PC-4702

| CONTENTS —                                   |

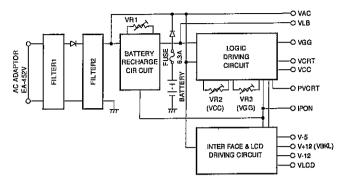

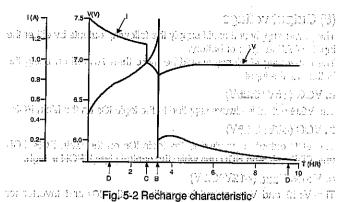

|----------------------------------------------|

| CHAPTER 1. OVERVIEW                          |

| CHAPTER 2. GENERAL INFORMATION 3             |

| CHAPTER 3. MAIN BOARD OPERATION              |

| CHAPTER 4. LCD UNIT                          |

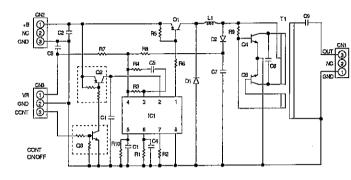

| CHAPTER 5. POWER SUPPLY CIRCUIT              |

| CHAPTER 6. HARD DISK                         |

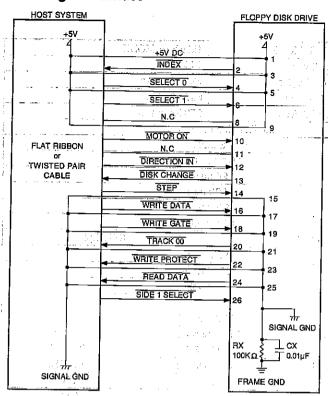

| CHAPTER 7. FLOPPY DISK DRIVE                 |

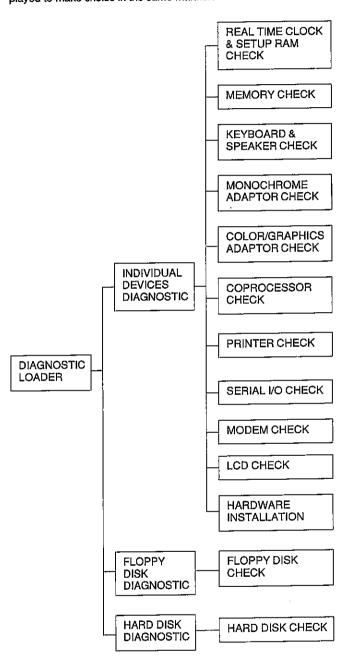

| CHAPTER 8. SERVICE-MAN DIAGNOSTIC            |

| CHAPTER 9. APPENDICES                        |

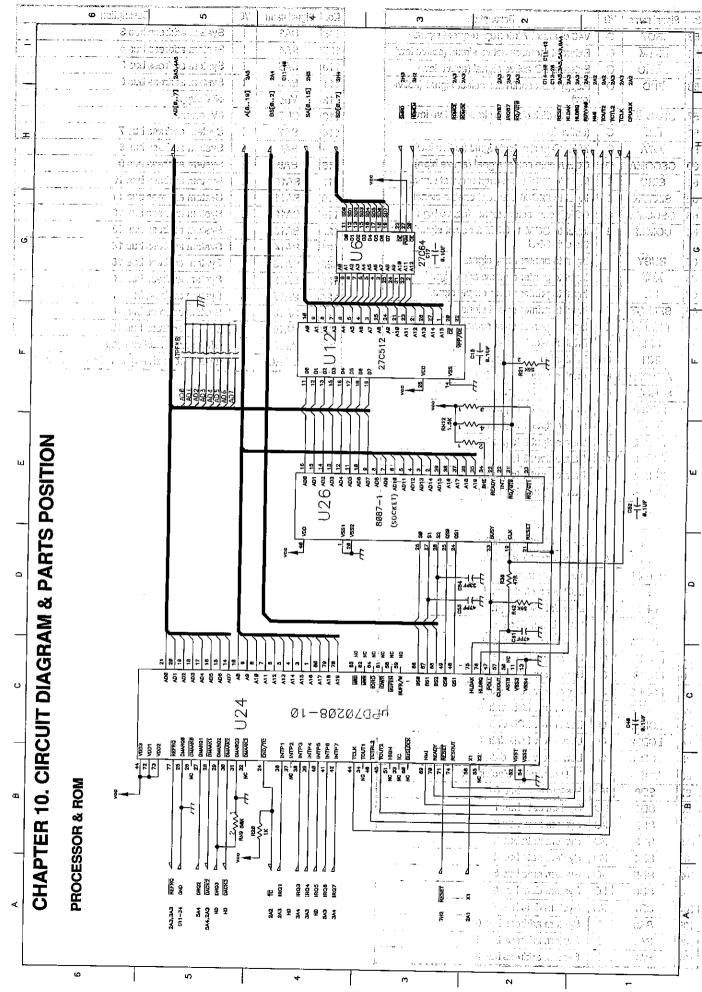

| CHAPTER 10. CIRCUIT DIAGRAM & PARTS POSITION |

### **CHAPTER 1. OVERVIEW**

### 1. Scope

This manual is covered for PC4702, PC4721, PC4741 CPU and hard disk drive.

For detailed information on other auxiliary equipment and options (list following), please refer to the separate service manuals provided for each devices.

- . CRT adaptor (CE-471A)

- MFD unit (CE-452F)

- EMS card (CE-471B)

- SIO card (CE-451B)

### 2. Service method

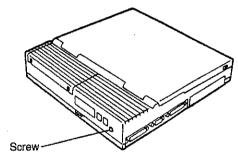

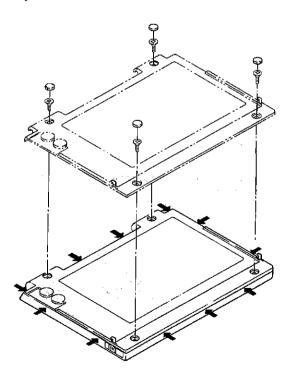

- 1) Cabinet Top Removal

- Before disassembly, remove the AC adaptor and the built-in lead battery.

If the CRT board, the modem board, or the SIO board is installed, locate the face plate screw fastened to the computer and remove.

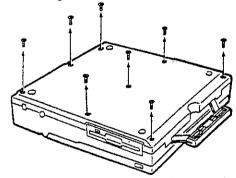

2. Remove the eight screws on the computer's bottom panel.

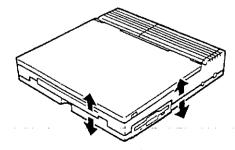

Lift up the cabinet top. This reveals the system board of the computer.

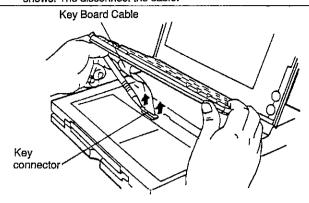

Lift up the keyboard and unfasten the connector as illustration shows. The disconnect the cable.

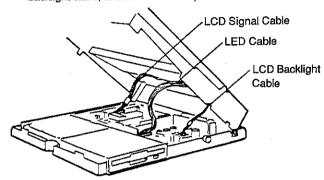

First incline the cabinet top backward slowly about 30 degrees.Then disconnect three cables. (the LCD signal cable, the LCD backlight cable, and the LED cable.)

- 2) LCD unit removal

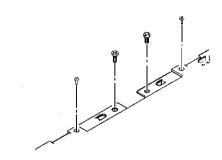

- 1. Remove the four screws which are fixing the tilt mechanism.

Move a tilt mechanism to the center with a screwdriver, and remove it upwards.

Then remove the other tilt mechanism in the same manner.

3. Operate the LCD release lever, unfix the upper cabinet and the LCD section, and separate the upper cabinet from the LCD section.

In this case, be careful not to damage two LCD cables.

### Installation

Install the upper cabinet and the LCD section by reversing the disassembly procedure.

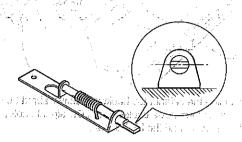

When installing the tilt mechanism, set the shaft horizontally in parallel to the angle bottom and insert into the LCD section.

- 2. Attach the upper and lower cabinets to the set.

- 3) LCD section

Disassembly

<Caution:

For disassembly of the LCD unit, be sure to follow the procedure below. If not, the cabinet may be damaged.

- 1. Remove the keyboard.

- 2. Separate the upper cabinet from the lower cabinet.

- 3. Remove the upper cabinet.

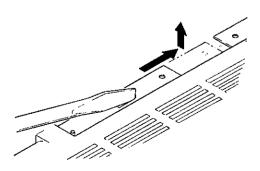

- Remove the four rubber cushions fixed with duplex tape on the LCD section, and remove the four screws which were covered by the four rubber cushions.

- 5. Remove the front and rear cabinets of the LCD section.

- 6. Remove the fixture which fixes the LCD section and the body.

- 7. Remove the reflection plate of the backlight.

- 8. Remove the fixing screws and the connectors of the illumination control PWB and the backlight convertor PWB, and remove the PWB's.

### Assembly

Assemble the LCD unit by reversing the disassembly procedure.

Carefully check that there is no fingerprint on the LCD section. If there is, clean with a cloth and alcohol. The cloth must be fine and smooth, such as glass wiper cloth.

- 2. Attach the upper cabinet to the set.

- 3. Attach the lower cabinet to the set.

- 4. Attach the keyboard to the set.

- HD INTERFACE AND HD DRIVE

The HD drive unit can be replaced only in whole unit, but not in part. When they are diagnosed to be defective by the diagnostic program, replace the whole unit of them.

### 4) Cautions

- Although the CE-471A CRT adaptor board is an option for the PC-4700, it comes standard for the US version PC-4700. For more information about the wiring schematics and parts layout, refer to the CE-471A Service Manual.

- Cosmetic sheet

Do not use the cosmetic sheet once removed. Be sure to use

the new one.

- Deposit of a paint dust on the back of the cabinet may fall on the PWB when the machine is disassembled and re-assembled for servicing and it may then cause a machine malfunction. To avoid this, the machine internal must be cleaned whenever the machine is disassembled.

### CHAPTER 2. GENERAL

## **INFORMATION**

### 1. General information

PC-4700 series are compact and lightweight laptop computers. They pack the power and sophistication of desk-top models into the laptop size

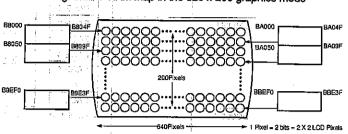

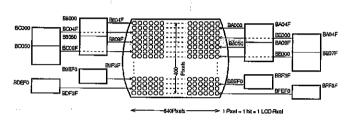

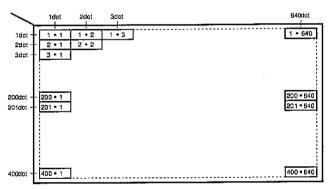

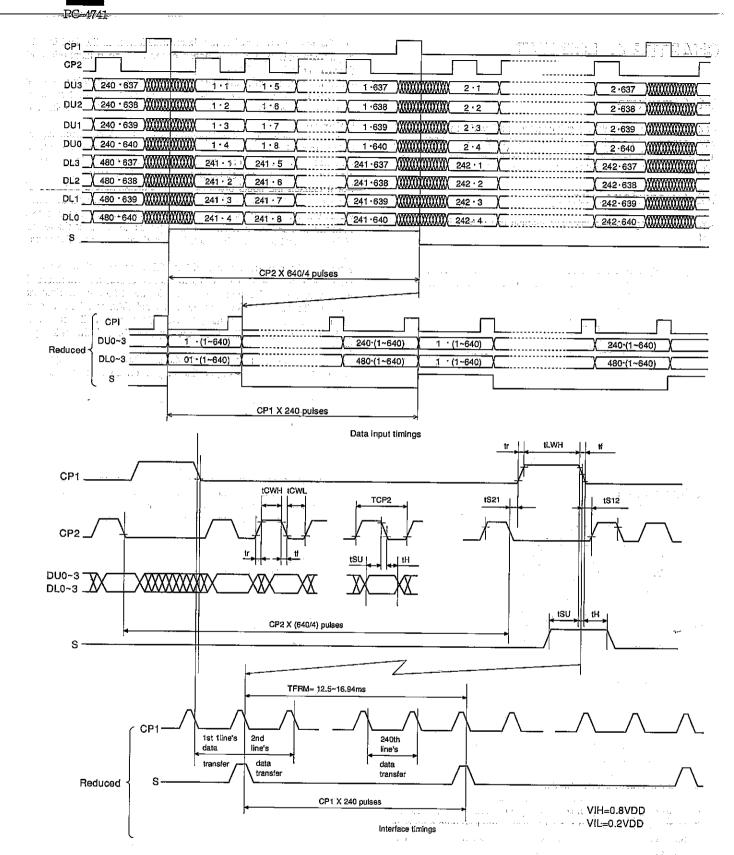

In order to attain the high performance, this computer accommodates large and high contrast paper white LCD with the CCFT backlight, 3-1/2" floppy disk drive, 3-1/2" hard disk drive, and well-packed 79-key full keyboard. The display provides clear text and graphics in 640 by 400 dots especially by supporting 4-shades of gray (tiling) and 8 x 16 dots (character box) characters.

Further, PC-4741 or PC-4721 incorporates a 40MB or 20MB hard disk drive in its unit and accomplish battery operation. The full-size step keyboard provides 79 keys, enhancing the ease of use with separate function and cursor keys.

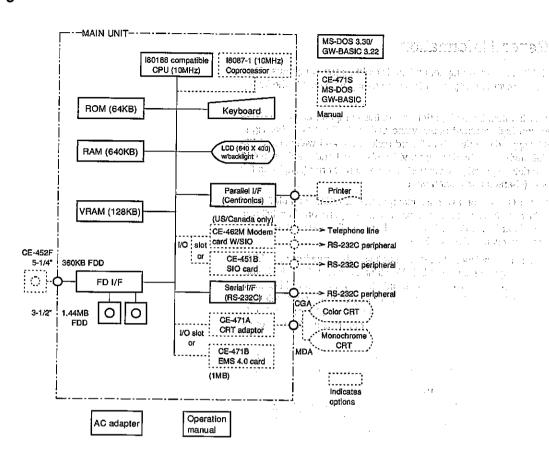

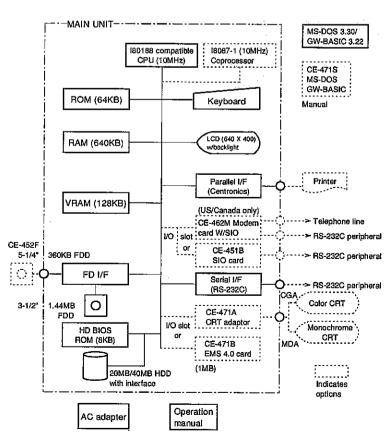

The main unit includes i80188 compatible CPU running at 10MHz, socket for coprocessor, 640KB RAM standard expandable to 1.6MB, a serial interface, a parallel printer interface, an external FDD interface. The internal options include modem card with a serial interface (for US/Canada only), color/monochrome CRT adaptor, and 1MB EMS memory card. The external expansions include 5-1/4" 360KB floppy disk drive unit.

The newly revised original BIOS assures the execution of numerous applications with the combination of MS-DOS 3.3 operating system.

PC-4700 series consists of the following 3 models:

- \*PC-4702: 640KB RAM; two 3-1/2" 1.44MB FDDs; display w/ back-light; 79-key keyboard; serial interface; parallel interface; external 5-1/4" FDD (360KB) interface; MS-DOS 3.30/GW-BASIC 3.22

- \*PC-4721: 640KB RAM; a 3-1/2" 1.44MB FDD; a 20MB HDD; display w/ backlight; 79-key keyboard; serial interface; parallel interface; external 5-1/4" FDD (360KB) interface; MSDOS 3.30/GW-BASIC 3.22

- \*PC-4741: 640KB RAM; a 3-1/2" 1.44MB FDD; a 40MB HDD; display w/ backlight; 79-key keyboard; serial interface; parallel interface; external 5-1/4" FDD (360KB) interface; MSDOS 3.30/GW-BASIC 3.22

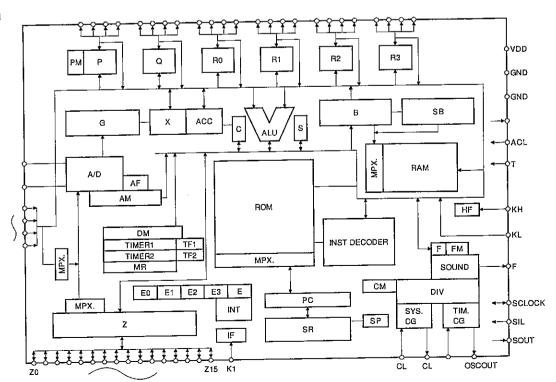

### 2. System Configuration

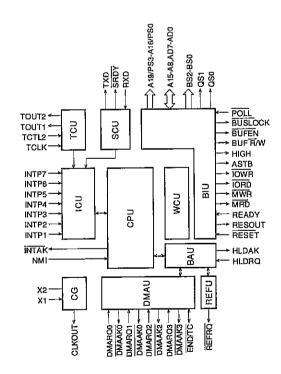

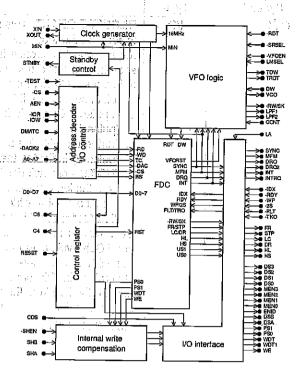

### 2-1. System block diagram

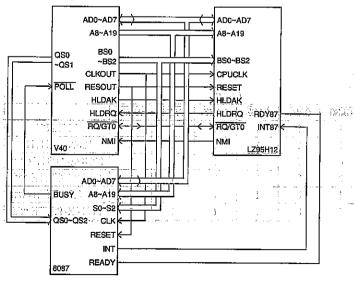

### 2-1-1. PC-4702

layelyed s. cekleral

MONTA VIEWA

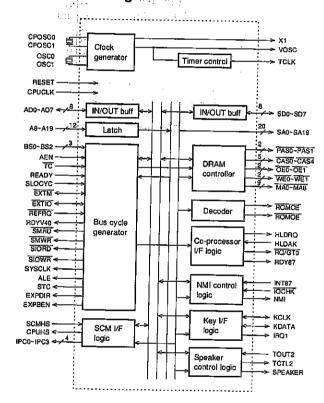

### 2-1-2. PC-4721/4741

### 2-2. Specification

2-2-1. Main unit

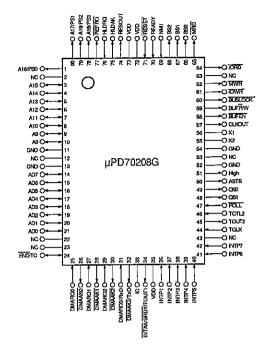

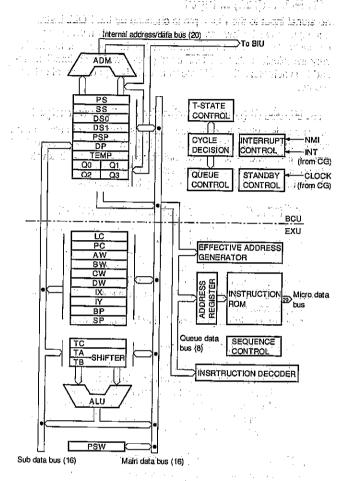

CPU

: NEC V40 (i80188 compatible)

CPU clock speed - 10MHz (7.16MHz when

coprocessor is installed.)

System speed - Standard/Slow selectable on set-up

menu

Coprocessor:

Socket for i8087-1 (10MHz version)

NOTE: CPU clock speed is changed to 7.16MHz

automatically when coprocessor is installed. When it is removed, CPU clock speed is

changed to 10MHz automatically.

Memory

: ROM - 64KB

including BIOS, set-up functions, CG, self check,

512K bits EP-ROM (27C512 type) x 1 piece

ROM-8KB (HD version only)

including HD BIOS 64Kbits EP-ROM (27C64

type) x 1 piece

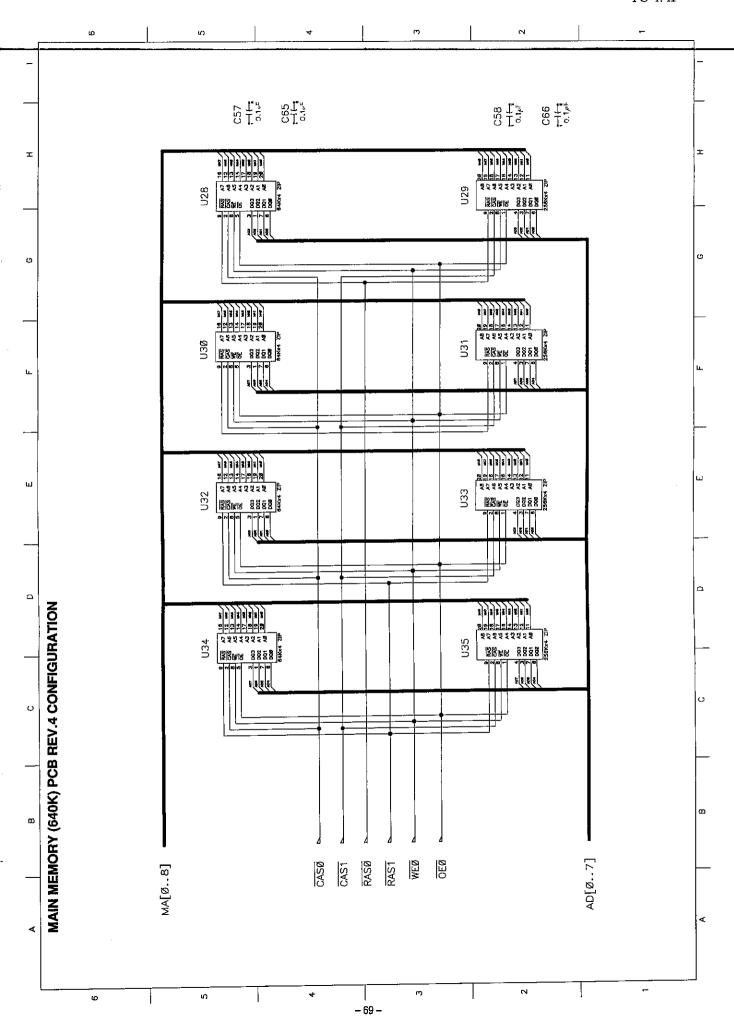

RAM - 640KB standard

256K bits (64K x 4 bits) DRAM x 4 pieces 1Mbits (256K x 4 bits) DRAM x 4 pieces

without parity

expandable up to 1.6MB with the optional 1MB

EMS memory card (EMS 4.0)

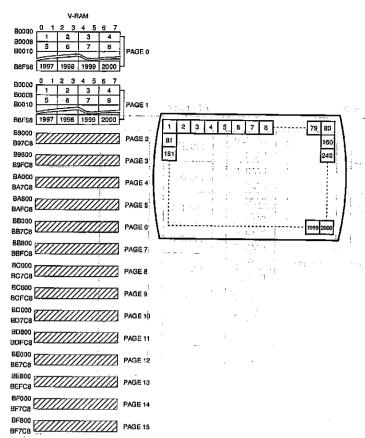

VRAM - 128KB

Display

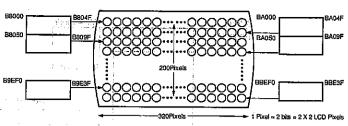

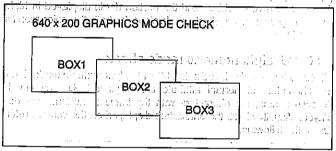

: TST (Triple Super Twisted nematic) LCD with one CCFT (Cold Cathod Flouecent Tube) edgelight Text - 80 char. x 25 lines, 8 x 16 dots char. Box Graphics - 640 x 400 pixels, 4-shades of gray (tiling)

Aspect ratio - 1:1

Emulation - CGA/MDA/AT&T 640 x 400 Graphics

LCD active area - 205(w) x 155(h) mm

LCD contrast and backlight brightness are adjus-

table by each volume

Not detachable

90 - 131 degrees tilt angle adjustment

**CCFT** backlight white color

life: Approx. 10,000 hours (until luminescent brightness becomes half)

can be replaced by service man (service parts)

Data storage: PC-4702 - two side-mounted 3-1/2" 1.44MB FDD

Right side: A drive, Left side: B drive

PC-4721/4741 - one side-mounted 3-1/2" 1.44MB FDD one internal 3-1/2" 20MB/40MB HDD

Left side: HDD (C drive), Right side:

FDD (A drive)

HDD - average access time: 29 msec

power save management:

can be set "Time-Out"" on set-up menu Always ON/2 minutes/5 minutes/10

minutes

\*: spindle motor of HDD will be controlled by the value of "Time-Out"

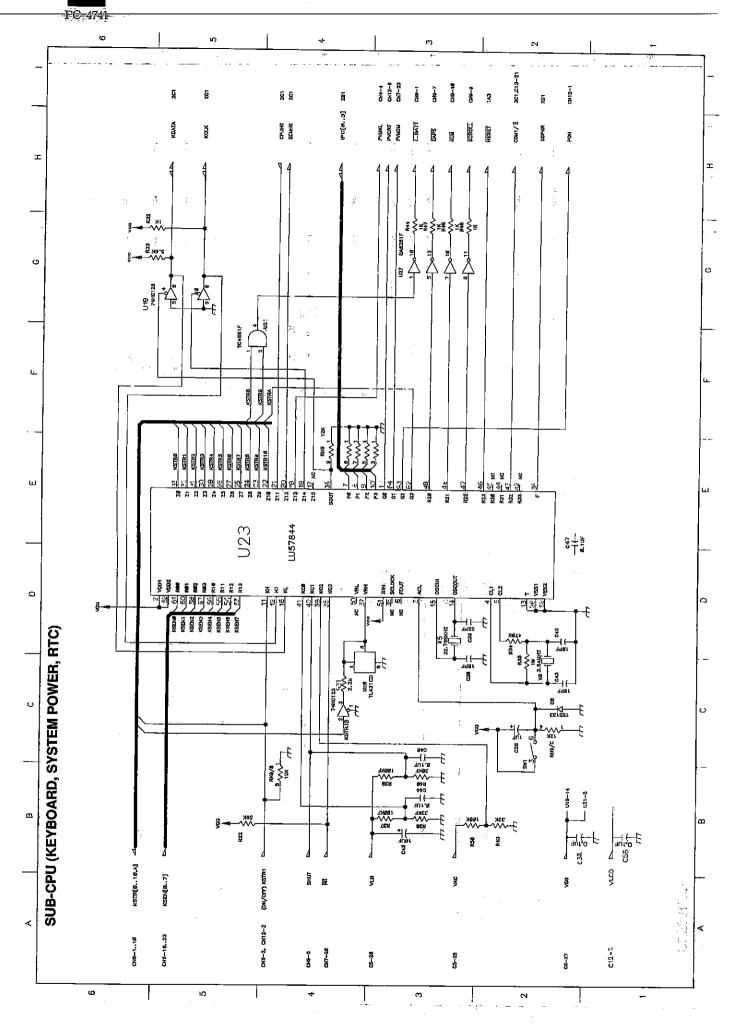

Keyboard

: full-size 79-key step keyboard

separate cursor keys

10 programmable function keys

LEDs for Num Lock, Scroll Lock, and Caps Lock

Set-Up key for pop-up set-up menu

Cylindrical and thin keytop With click mechanizm

Not detachable

Interface : Serial (RS-232C) x 1 port (D-SUB 9 pin, male con-

Parallel (Centronics) x 1 port (D-SUB 25 pin, female

connector)

I/O slot

pin, female connecter) : Sharp proprietary slot x 3

1 slot for color/monochrome CRT adaptor

1 slot for modem/SIO card (for US/Canada only)

External 5-1/4" FDD (360KB) x 1 port (D-SUB 25

or SIO card

The above cards are installed into the same space. So, only one card is available at the same time.

- 1 slot for 1MB EMS 4.0 memory card

Power Supply: Rechargeable lead battery

low battery warning low battery indicator

alarm AC adaptor EA-452V

IN

local voltage

OUT Dimension DC 9V, 2.5A

115(w) x 67(d) x 55(h) mm

Weight

Approx. 425g

Volume

: LCD contrast volume

Backlight brightness volume

Switch

: Power ON/OFF button (software switch)

4 dip switches

| Dip Switch Label | Feature                                                 | Initial setting |

|------------------|---------------------------------------------------------|-----------------|

| 1                | Alarm Control<br>(Low Battery/Shut off Alarm)<br>ON/OFF | ON              |

| 2                | Speaker Control<br>(without alarm) ON/OFF               | ON              |

| 3                | System all reset ON/OFF                                 | OFF             |

| 4                | Speaker Volume LOW/HIGH                                 | OFF (HIGH)      |

Shut off alarm switch (alarm when upper cabinet is shut during power

LED indicator: Power (green); low battery (red);

PC-4702 - drive A (green); drive B (green)

PC-4721/4741 - floppy disk (green); hard disk

Caps Lock (green); Num Lock (green); Scroll Lock

(green)

Other

; Carrying handle; speaker; display lock slide-switch x

Dimension

: 11(w) x 11.1(d) x 2.2(h) inch 280(w) x 282(d) x 58(h) mm

(high: cushion rubber on the bottom cabinet in-

cluded, without cushion rubber: 57mm)

Weight

: PC-4702 - 3.6kg

PC-4721/4741 - 3.8kg

(with battery, without AC adaptor)

battery: Approx. 830g

AC adaptor (EA-452V): Approx. 425g

Software Manual

MS-DOS 3,30/GW-BASIC 3,22

Operation Manual (MS-DOS/GW-BASIC quick refer-

ence included) Optional MS-DOS and GW-BASIC manuals

valuation."

# 2-2-2: Option to (Bland) Gill "Wild Female I

Internal Options:

CE-471A color/monochrome CRT adaptor

color/monochrome 2 modes supported color: CGA (640 x 200 pixels) monochrome: MDA (720 x 350 pixels)

color/monochrome mode is selected by set-up functions.

par, formale contracted)

2 character sets (CG1/CG2) supported CG1:general CG2: Denmark/Norway

CG1/CG2 is selected by short-pin switch on the card.

dealer option

CE-451B SIO card

armig - Serial (RS-232C) x 1 port (D-SUB 25pin, male connector)

dealer option

NOTE: Max. SIQ 2 ports available when CE-451B installed.

1. Standard SIO (D-SUB 9pin, male connector)

2. SIO on the optional CE-451B SIO card (D-SUB 25pin. male connector)

มีประกอบที่ ราชยับ ได้เกิดไ

Maria Na

CE-471B EMS memory card

1MB EMS 4.0 memory card and EMS 4.0 software with operation manual

dealer option

CE-462M modern card (for US/Canada only)

mode/SIO 2 functions supported

mode: 300/1200/2400 BPS; Bell 103/212A; CCITT V.21, V22 and V.22 bis

Haves compatible command set

SIO: RS-232C x 1 port (D-SUB 25 pin, male connector) modem/SIO function is selected by set-up functions

dealer option

with installation instructions

NOTE: Max. SIO 2 ports available when CE-462M is installed and used as a SIO. Early model to care

1. Standard SIO (D-SUB 9 pin, male connector)

2. SIO on the optional CE-462M modern card (D-SUB 25 pin, male connector)

External options:

CE-452F 5-1/4" FDD unit (without SEEG)

- 5-1/4" FDD (360KB) x 1

AC power

with I/F cable

### Manual:

CE-470KE/F/W/M/S key top kit

- key top (E: 18, F: 21, W: 19, M: 19, S: 24 pieces)

tool for pulling up the key top

CE-470SE/F/G/I operation manual

operation manual for PC-4700 series (E: English, F: French, G: German, I: Italian)

NOTE: PC-4700 for SEEG doesn't include the operation manual.

TO SECTION AND SECTION AND SECTION AND SECTION AND SECTION ASSESSMENTS.

ngruumma pi pedikidi jaga eti libekidi sengiga j

Landy Style 1 of the Landy

Main mall 1-2 S tolds...gares and oal) out vice tot orden (affiliation) (MINO) — periode (faction at 10 (Confit Decrease are seen per รู และ เขาประกรท์นา พระศักร์เกรสรา และแบบ ทั้งส Doses for Lorent (1997) western, [1997] - 1940 God, apeda as dicercal - 1997 God ราช (ค.ศ. 2012) วิทย์ได้รับที่ การกรรรสสากสถาสลาสหาร์ที่หนึ่งผู้สือสอดสาวสอน a brain than H. W. Breeze a secretary vicesionship to third of regrisors  $(\omega, N) \times V(N) \simeq$ to 4 to 100 manifesting to the public of The second of th i verno raci a ovadi i palaže Mitasi. Perno raci a ovadi i palaže Mitasi. The second of the product buir Traffia) - av -1957年9月2日在日本市大学的中央工作。 医乳腺性 医髓膜 医二种电影 and the second s 2007/00/15 The State of Republic Control - 5 i i History and the second

er (m. 1945). Marie er (m. 1946). وينور والمعاوية والمحاوروس وتواهم خيجتني makinta a wata be maniford that it was a more as an

$w_1,\dots,w_{2^{n-1}-1},\dots$

the term of the first own countries.

Contracted an alternative ball et a a juliot et post a vene policie. Poly vi mati (was te a stive) orse, aktian deligation

or the Alberta Control of the Alberta

of the feat of a

## **CHAPTER 3. MAIN BOARD OPERATION**

### 3-1. Memory and I/O map

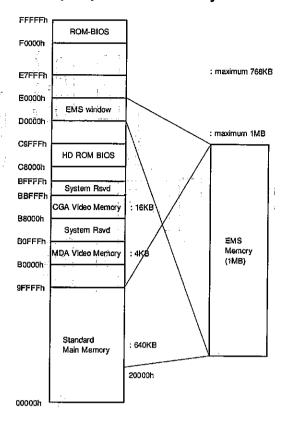

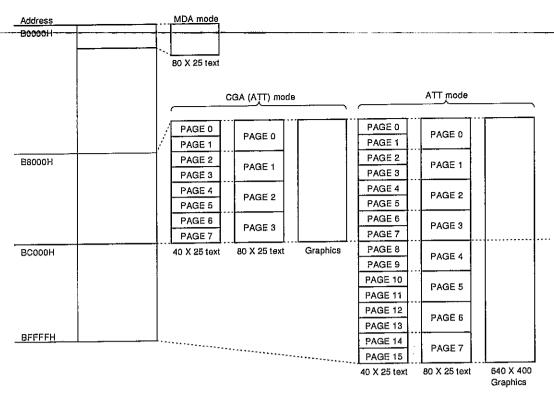

### 3-1-1. Memory map for the PC-4700 system

Fig. 3-1 Overall memory map

### 3-1-2. IO/MAP

| Register                               | IO Address. |

|----------------------------------------|-------------|

| Emulated DMA Controller                | 00H0FH      |

| V40DMA Controller                      | 10H1FH      |

| Interrupt Controller                   | 20H3FH      |

| System Timer                           | 40H5FH      |

| PPI                                    | 60H62H      |

| NMI Mask                               | A0HBFH      |

| Asynchronous Communication (Secondary) | 2F8H2FFH    |

| Hard Disk                              | 320H323H    |

| Parallel Port                          | 378H37FH    |

| Parallel Port                          | 3BCH3BEH    |

| VIDEO IO                               | 3B0H3BBH    |

| VIDEO IO                               | 3BFH        |

| VIDEO IO                               | 3C0H3CFH    |

| VIDEO IO                               | 3D0H3DFH    |

| FLOPPY DISK IO                         | 3F0H3F7H    |

| Asynchronous Communication (Primary)   | 3F8H3FFH    |

| V40 System IO                          | FFF0HFFFFH  |

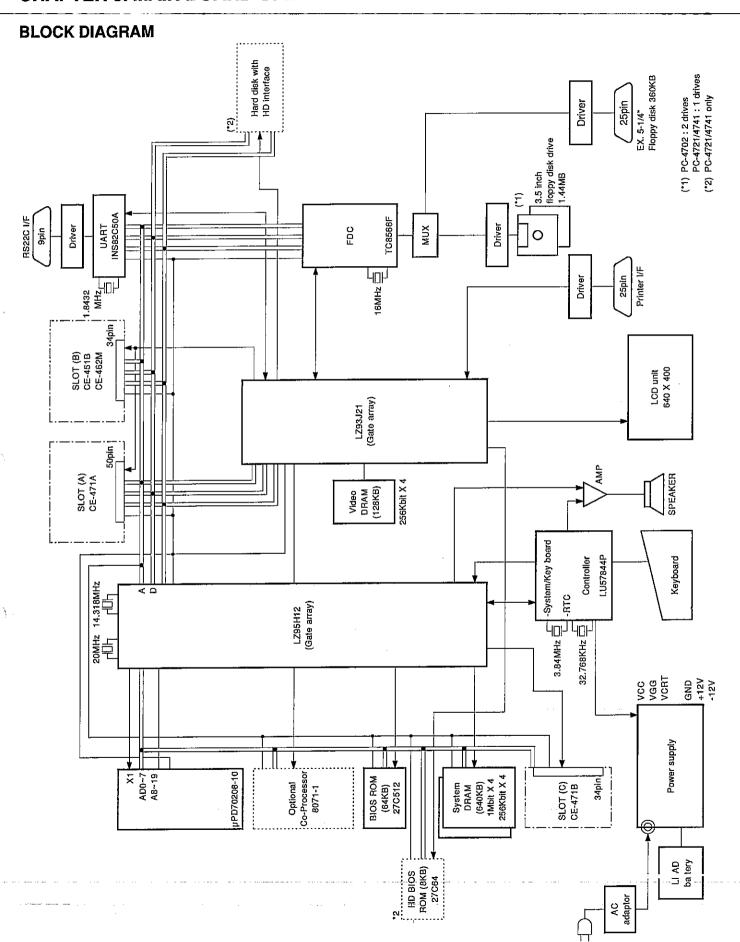

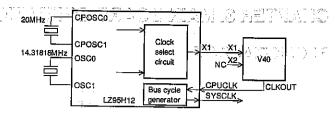

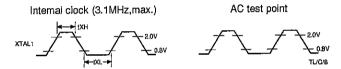

### 3-2. Clock generator

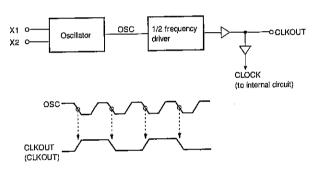

The clock generator is included in LZ95H12, and connected with two crystal oscillators of 14.31818MHz and 20MHz.

The two clocks pass through the clock select circuit in LZ95H12, and one of them is outputted from X1 terminal to V40 X1 terminal. The details are shown in Fig. 3-2.

Fig. 3-2 Overall clock generate circuit

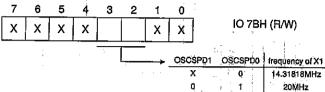

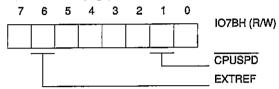

The frequency of the clock supplied from LZ95H12 X1 terminal to V40 is determined according to the states of bit 3 (OSCSPD1) and bit 2 (OSCSPD0) of the IO port (7BH) in LZ95H12 as shown below.

Assertion of the RESET signal will reset OSCSPD [0..1]. IF 8087 is not installed, ROM-BIOS sets OSCSPD0.

When setting OSCSPD0, the shift to frequency of 10MHz is made with no glitches, thus avoiding the need to reset the system.

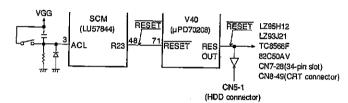

### 3-3. Reset circuit

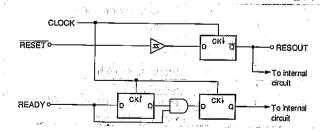

Fig. 3-3 Reset control circuit

The SCM can be reset in one of the following two ways.

- When VGG turns on, a high state of signal is sent to the line ACL of the SCM from the differentiation circuitry composed of a capacitor and resistor.

- When the dip switch-1, located at the lower side of the machine, set ON, it causes the ACL input high to reset the SCM. Operation starts when it turned off.

With depression of the ON/OFF switch while the machine is off or a hardware reset is given (simultaneous depression of CTRL, ALT, SETUP keys), VCC is turned active and RESET is forced high. The V40 synchronizes an async signal RESET with the internal clock and sends it out as an active high signal.

The former (RESET) is sent to the V40, and the latter (RESET) to the LZ95H12, LZ93J21, TC8566F, 82C50AV, 34-pin slot, CRT connector. The RESET signal is inverted and sent to HDD connector.

### 3-4. Interrupt control

Eight maskable interrupts and one non-maskable interrupt are provided.

- NMI is set high by the LZ95H12 when a specific I/O is accessed.

- Maskable interrupt may be caused in one of the following:

| Number | Usage                                  | Originating device   |  |

|--------|----------------------------------------|----------------------|--|

| 1 .    | Keyboard                               | LZ95H12              |  |

| 3      | Asynchronous communication (Secondary) | - INS82C50A          |  |

| 4      | Asynchronous communication (Primary)   | INS82C5UA            |  |

| 5      | Hard disk                              | Hard disk controller |  |

| 6      | Floppy disk                            | TC8566F              |  |

| 7      | Parallei printer                       | LZ93J21              |  |

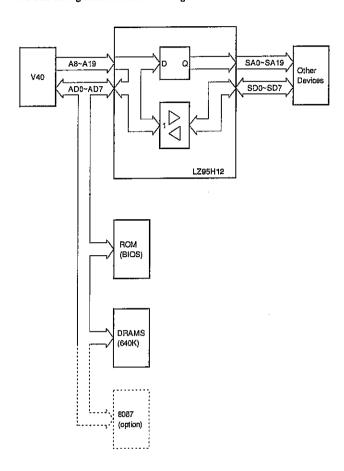

### 3-5. Bus configuration

The PC-4700 system uses the forrowing two buses.

- 1) CPU (AD) bus

- 2) System Data (SD) bus

The bus configuration is shown in Figure 3-4.

Fig. 3-4 Bus configuration

### 3-6-2. LZ95H12 address assignment

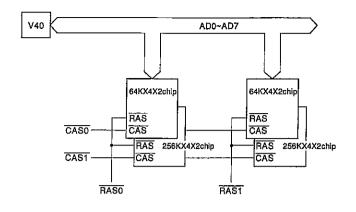

$\overline{RAS}$  and  $\overline{CAS}$  are generated from LZ95H12.  $\overline{RAS0}$  is set active if  $\overline{RAS}$  is even address or  $\overline{RAS1}$  active if  $\overline{RAS}$  is odd address.

CAS signal is assigned to CAS0 ~ CAS4 as shown in Table 3-1.

### Table 3-1

| Input Ou |          |        |     |    |       |      | )utput |      |      |      |      |      |       |                    |

|----------|----------|--------|-----|----|-------|------|--------|------|------|------|------|------|-------|--------------------|

| A19      | A18      | A17    | A16 | A0 | REFRQ | RAS0 | RAS1   | CAS0 | CAS1 | CAS2 | CAS3 | CAS4 | ROMCE |                    |

| X        | Х        | Х      | Х   | Х  | 0     | 0    | 0      | 1    | 1    | 1    | 1    | 1    | 1     | REFRESH            |

| 1        | 1        | 1      | 1   | х  | 1     | 1    | 1      | 1    | 1    | 1    | 1    | 1    | 0     | F0000H~FFFFFH      |

| 0        | 0        | 0      | Х   | 0  | 1     | 0    | 1      | 0    | 1    | 1    | 1    | 1    | 1     | 00000H~1FFFFH even |

| 0        | 0        | 0      | Х   | 1  | 1     | 1    | 0      | 0    | 1    | 1    | 1    | 1    | 1     | 00000H~1FFFFH odd  |

| Neither  | of A19 ~ | A17 is | Х   | 0  | 1     | 0    | 1      | 1    | 0    | 1    | 1    | 1    | 1     | 20000H-9FFFFH even |

| "0"      |          |        | Х   | 1  | 1     | 1    | 0      | 1    | 0    | 1    | 1    | 1    | 1     | 20000H~9FFFFH odd  |

### 3-6. Memory

### 3-6-1. Block diagram

Fig. 3-5 RAM section block diagram

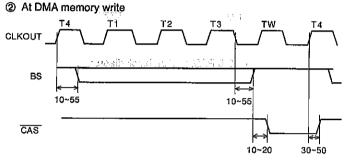

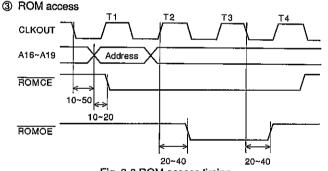

### 3-6-3 Memory access timing

OE,WE

RAS

OE,WE

RAS

30~40

MA

ROW Address

Column Address

30~40

t-C. Memory

Fig. 3-6 DRAM access timing (normal)

Same as ① for the timing of OE, WE, RAS, and MA.

Fig. 3-7 DRAM access timing (DMA memory write)

Fig. 3-8 ROM access timing

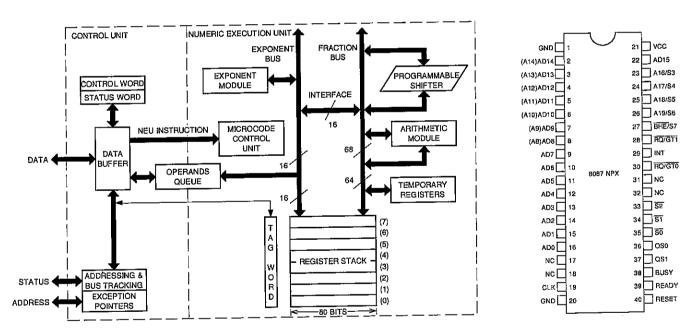

### 3-7. 8087 interface

The interface log of 8087 is stored in LZ95H12. The signal connection is shown in Fig. 3-9.

Fig. 3-9 8087 interface signal connection

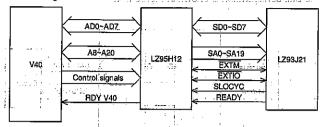

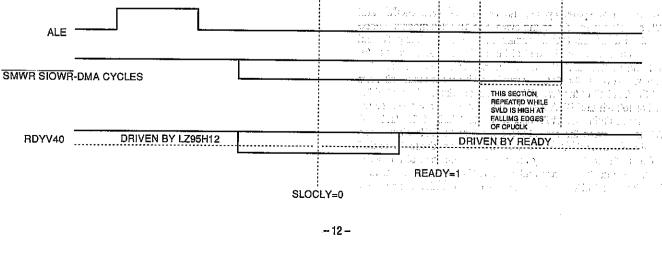

### 3-8. READY control circuit

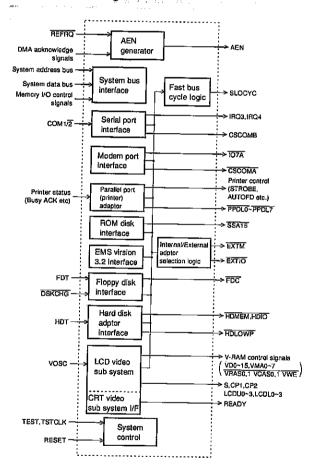

The signal READY (RDYV40) for V40 is controlled by LZ95H12. LZ95H12 and LZ95J21 control EXTM, EXTIO, SLOCYC, and READY signals for the devices accessed. LZ95H12 determines the bus cycle according to these signals, to control RDYV40. The block diagram is shown in Fig. 3-10.

3-8. Run occiliantellum

Fig. 3-10 Overall ready control signals

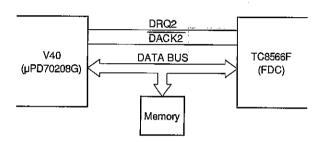

### 3-9. DMA control

Although the V40 has four DMA channels, two channels are used. DRQ2 and DACK2 are used for controlling the floppy.

Fig. 3-11 Overall DMA control signals

When the V40 starts to DMA after setting the TC8566F register, the TC8566F sets DRQ2 high. After the V40 receives this signal, DACK2 is set low to perform DMA transfer between the TC8566F and the memory.

DRQ3 and DACK3 are used for controlling the hard disk. DRQ3 is supplied from the LSI in the hard disk controller. When DRQ3 becomes high, V40 makes DACK3 low to perform DMA transfer between with the controller.

### 3-10. Bus cycle generator (including LZ95H12)

### 3-10-1. General

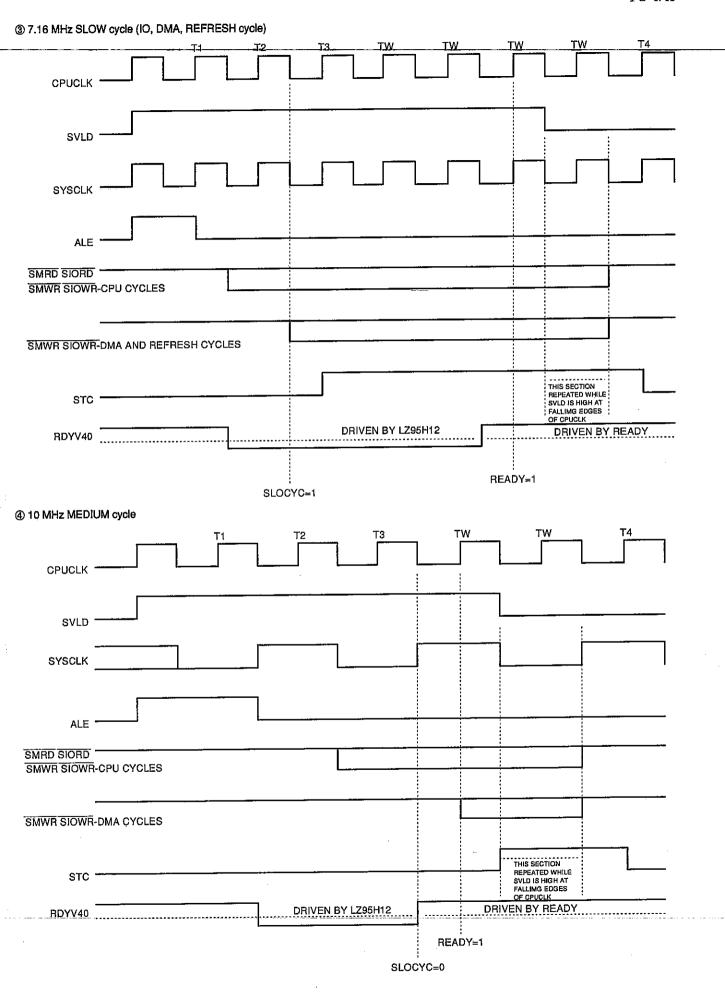

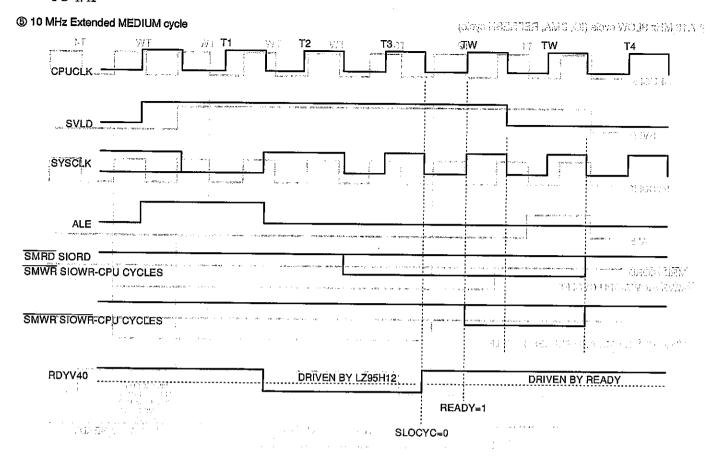

The LZ95H12 bus cycle generator produces the SYSCLK, ALE, STC, SMRD, SMWR, SIORD and SIOWR signals. It interprets the READY signal and drives the RDYV40 signal to control the number of wait states. The LZ95H12 determines the speed of the devices involved in the transfer. Devices are grouped into three speed categories:

- 1. fast AD bus devices:

- 2. fast SD bus devices; and

- 3. slow SD bus devices.

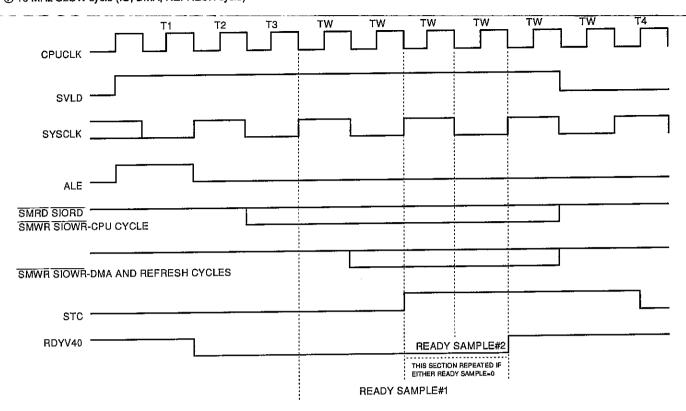

Fast AD devices are the V40, the 8087, the LZ95H12, the system ROM, the system DRAM. Fast SD bus devices are those devices which are controlled by the LZ93J21 for which the SLOCYC signal is not asserted. This signal is sampled at the start of first T-cycle following the assertion of the SMRD, SMWR, SIORD or SIOWR. At 7.16MHz, this occurs at the start of T3. At 10 MHz this occurs at the start of the first TW. All other devices are slow SD bus devices.

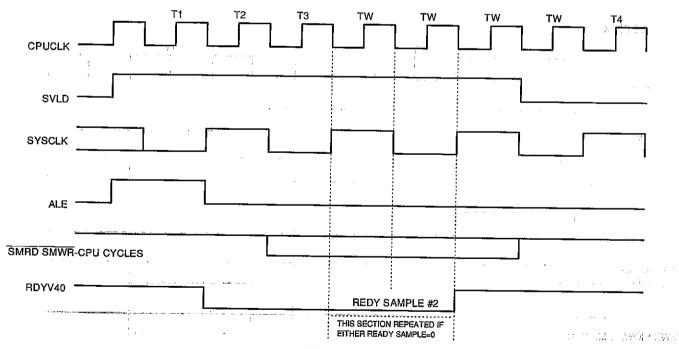

There are three speeds of non-refresh cycles: fast, medium and slow. Fast speed cycle execute with no wait states, except for IO, NMI trapping cycles, which take nine T-cycles. Medium speed cycles may also insert wait states in response to a reset READY signal. A special extended medium speed cycle that drives SYSCLK from CPUCLK is also implemented. At 7.16 MHz, the minimum medium speed cycle takes 5 T-cycles. At 10 MHz, the minimum medium speed cycle takes 6 T-cycles. Medium and slow speed cycles have the same timing until SLOCYC is sampled.

If the CPUSPD (IO7BH bit 1) bit is set, the bus cycle generator will only generate slow speed memory cycles. This is done to accommodate programs using software timing loops. Assertion of the RESET signal will reset CPUSPD. If CPUSPD is reset, then speed of the cycle is dependent on the slowest device involved. If the slowest device is a fast AD bus device then a fast speed cycle is generated. If the slowest device is a fast SD bus device, then a medium speed cycle is generated. Otherwise, a slow speed cycle is generated. When "speed: slow" is selected in the set up menu, CPUSPD = 1 (High)

There are two speeds for refresh cycle-fast and slow. If the EXTREF (IO7BH bit 6) bit is set, the bus cycle generator will generate a slow speed cycle. Thus DRAM on the SD bus may be refreshed. If EXTREF and CPUSPD are reset, then the bus cycle generator will generate a fast speed cycle. Thus any DRAM on the SD bus must provide its own refresh. Resetting EXTREF may result in as much as a 5% increase in system throughput. Assertion of the RESET signal will reset EXTREF. When the optional EMS card (CE-453B) is installed, EXTREF = 1 (High).

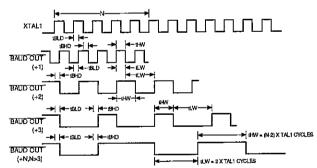

### 3-10-2. SYSCLK Generation

For 7.16 MHz cycles, CLKOUT drives SYSCLK.

For 10 MHz fast speed cycles, SYSCLK is set during T2 and is reset during the rest of the cycle. For 10 MHz medium speed cycles, SYSCLK is set during T2, the first TW and T4 and is reset during the rest of the cycle. For 10 MHz extended medium speed cycles, SYSCLK is set during T2 and driven by CPUCLK for the rest of the cycle. For 10 MHz slow speed cycles, SYSCLK is set during T2, during the odd TW's and during T4 and is reset during the rest of the cycle. There are always an even number of TW's in a 10 MHz slow speed cycle. For 10 MHz cycles, SYSCLK is always reset during TI's and interrupt acknowledge cycles.

# 3-10-3. SWRD, SMWR, SIORD and SIOWR Generation

SMRD and SMWR are not asserted during non-refresh cycles that access fast AD bus memory devices. SIORD and SIOWR are not asserted during non-refresh cycles that access LZ95H12 internal IO devices or V40 internal private IO devices. SIORD and SIOWR are asserted during accesses to emulated MDA/CGA IO addresses. SMRD and SIOWR are not asserted during fast refresh cycles.

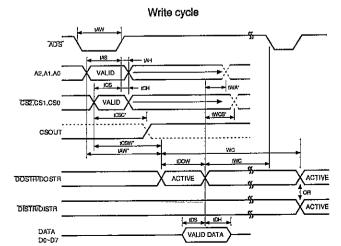

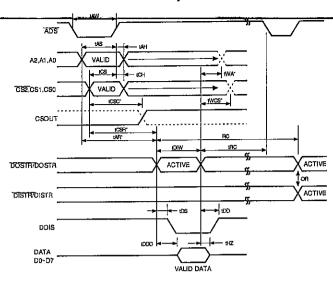

For 7.16 MHz cycles, the SMRD and SIORD signals may be reset during T2, T3 and TW. These signals are set during the rest of the cycle. The same is true for SMWR and SIOWR during non-refresh, non-DMA cycles. For DMA memory write cycles, the SMWR signal may be reset during T3 and TW. SIOWR is set during the rest of the cycle. For refresh and DMA memory read cycles, the SIOWR signal may be reset during T3 and TW. SIOWR is set during the rest of the cycle.

For 10 MHz fast speed cycles, the SMRD, SMWR, SIORD and SIOWR signals are set during the cycle. For 10 MHz medium speed cycles, the SMRD and SIORD signals may be reset during T3 and TW. They are set during the rest of the cycle. The same is true for SMWR and SIOWR during non-refresh, non-DMA cycles. For DMA memory write cycles, the SMWR signal may be reset during all TW's except the first half of the first TW SMWR is set during the rest of the cycle. For refresh and DMA memory read cycles, the SIOWR signal may be reset during all TW's except the first half of the first TW. SIOWR is set during the rest of the cycle. For 10 MHz slow speed cycles, the SMRD and SIORD signals may be reset during T3 and all TW's except the last TW. They are set during the rest of the cycle. The same is true for SMWR and SIOWR during non-refresh, non-DMA cycles. For DMA memory write cycles, the SMWR signal may

be reset during all TW's except the first TW and last TW. SMWR is set during the rest of the cycle. For refresh and DMA memory read cycles, the SIOWR signal may be reset during all TW's except the first TW and last TW. SIOWR is set during the rest of the cycle.

# 3-10-4. READY Interpretation and RDYV40 Generation

During fast speed cycles RDYV40 is set. RDYV40 is set during T1 and Ti.

For 7.16 MHz medium speed cycles, RDYV40 is reset during T2 and then READY drives RDYV40 during the rest of the cycle. For 7.16 MHz slow speed CPU/COP memory cycles, RDYV40 is reset during T2 and T3 and then RDYV40 is driven by READY during the rest of the cycle. For 7.16 MHz slow speed IO, refresh and DMA cycles, RDYV40 is reset during T2, T3 and the first two TW's and then RDYV40 is driven by READY during the rest of the cycle.

For 10 MHz medium speed cycles, RDYV40 is reset during T2 and T3 and then RDYV40 is driven by READY during the rest of the cycle. For 10 MHz slow speed CPU/COP memory cycles, RDYV40 is reset during T2, T3 and the first two TW's. READY is sampled at the start and the end of the odd TW's starting with the first TW. If READY is reset for either sample, then RDYV40 remains reset for two more T-cycles and READY is again sampled. If READY is set for both samples, then RDYV40 remains reset for two more T-cycles and is then set for the rest of the cycle. For 10 MHz slow speed CPU/COP IO, refresh and DMA cycles, RDYV40 is reset during T2, T3 and the first four TW's, READY is sampled at the start and the end of the odd TW's starting with the third TW. If READY is reset for either sample, then RDYV40 remains reset for two more T-cycles and READY is again sampled. If READY is set for both samples, then RDYV40 remains reset for two more T-cycles and is then set for the rest of the cycle.

### 3-10-5. STC Generation

During fast speed cycles, STC is reset.

For 7.16 MHz medium and slow speed cycles, STC is driven by the inverted value of TC.

For 10 MHz medium speed cycles, STC is set during the second and subsequent TW's and during T4 while TC is reset. For 10 MHz slow speed cycles, STC is set during the third and subsequent TW's and during T4 while TC is reset. STC is reset during the rest of the cycle.

### 6 10 MHz SLOW cycle (CPU-MEMORY cycle)

SLOCYC=1

READY SAMPLE #1

The state of the second second

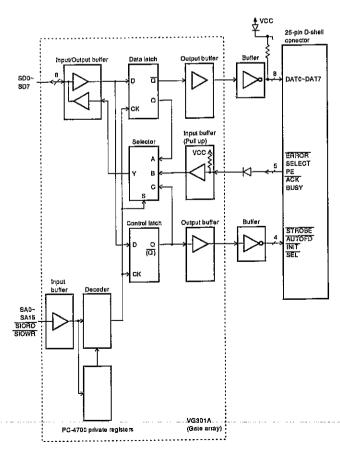

### 3-11. Printer interface

Fig. 3-12 shows a functional block diagram of the printer interface circuit. This circuit consists of the print data register, printer status port and printer control register.

The print data register, which is assigned at the I/O address 378H or 3BCH, stores data to be sent to the printer. The contents of this register can be read by the CPU at the I/O address 378H or 3BCH via the buffer.

The printer status port reads status information sent from the printer. This port is assigned at the I/O address 379H or 3BDH.

The printer control register stores control codes to be sent to the printer. This register assigned at the I/O address 37AH or 3BEH. Bit 4 of this register determines whether the  $\overline{ACK}$  signal from the printer makes enable or disable as the CPU interrupt signal. When this bit is HIGH, interruption is enabled.

The contents of this register can be read by the CPU at the I/O address 37AH or 3BEH.

Assignment of the printer interface I/O address to either 37XH or 3BXH is dependent on the state of PPSEL (parallel port select bit 4) of the PC-4600 register CFR (Configuration Register) which is assigned to the I/O address 7FH. If PPSEL is 0, the printer interface I/O address is assigned to 3BXH. If PPSEL is 1, the address is assigned to 37XH.

It is possible to disable the standard printer adaptor by resetting PPS (bit 1) of the PCR (Planar Control Register) I/O address 65H which is normally set on.

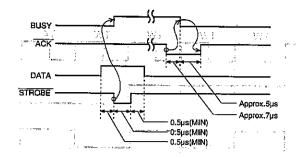

Table 3-2 shows the printer I/O address definition. Fig. 3-13 shows the printer timing chart.

Fig. 3-12 Function block diagram

Fig. 3-13 Timing chart

| I/O Address Read/ Write Bit Description  65H R/W 1 PPS. 1: Enables the standard print adaptor (normally set 1).  7FH R/W 4 PPSEL (Parallel Port Select) 0: Printer adaptor I/O address assigned to 36XH. 1: Printer adaptor I/O address assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)  3BCH 0 I Print data 1 | ess |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1: Enables the standard print adaptor (normally set 1).  7FH R/W 4 PPSEL (Parallel Port Select) 0: Printer adaptor I/O addre is assigned to 36XH. 1: Printer adaptor I/O addre is assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)                                                                              | ess |

| adaptor (normally set 1).  7FH R/W 4 PPSEL (Parallel Port Select) 0: Printer adaptor I/O addre is assigned to 36XH. 1: Printer adaptor I/O addre is assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)                                                                                                            | ess |

| 0: Printer adaptor I/O addre is assigned to 36XH. 1: Printer adaptor I/O addre is assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)                                                                                                                                                                              |     |

| is assigned to 36XH.  1: Printer adaptor I/O addre is assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)                                                                                                                                                                                                          |     |

| 1: Printer adaptor I/O addre is assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)                                                                                                                                                                                                                                | 988 |

| is assigned to 37XH.  PPSEL R/W 0 Print data 0 (LSB)                                                                                                                                                                                                                                                             | 988 |

| PPSEL R/W 0 Print data 0 (LSB)                                                                                                                                                                                                                                                                                   |     |

| - 1 1111 GENERAL D (LOB)                                                                                                                                                                                                                                                                                         |     |

|                                                                                                                                                                                                                                                                                                                  |     |

| 2 Print data 2                                                                                                                                                                                                                                                                                                   |     |

| 3 Print data 3                                                                                                                                                                                                                                                                                                   | _   |

| 4 Print data 4                                                                                                                                                                                                                                                                                                   |     |

| 378H 1 5 Print data 5                                                                                                                                                                                                                                                                                            |     |

| 6 Print data 6                                                                                                                                                                                                                                                                                                   |     |

| 7 Print data 6                                                                                                                                                                                                                                                                                                   |     |

| PPSEL R 0 Not used (0 read)                                                                                                                                                                                                                                                                                      | -   |

|                                                                                                                                                                                                                                                                                                                  |     |

| 3BDH 0 1 Not used (0 read) 2 0 or 1 read                                                                                                                                                                                                                                                                         |     |

| 3 ERROR read                                                                                                                                                                                                                                                                                                     | _   |

|                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                  |     |

| 5 PE read                                                                                                                                                                                                                                                                                                        |     |

| 6 ACK read                                                                                                                                                                                                                                                                                                       |     |

| 7 BUSY read PPSEL R/W 0 STROBE written                                                                                                                                                                                                                                                                           |     |

|                                                                                                                                                                                                                                                                                                                  |     |

| 1 Notor B written                                                                                                                                                                                                                                                                                                |     |

| 2 INIT written                                                                                                                                                                                                                                                                                                   |     |

| 3 SEL written                                                                                                                                                                                                                                                                                                    |     |

| 37AH 1 4 !RQENA, 1: Enables interrupt request.                                                                                                                                                                                                                                                                   | t   |

| 5 Not used (0 read)                                                                                                                                                                                                                                                                                              |     |

| 6 Not used (0 read)                                                                                                                                                                                                                                                                                              |     |

| 7 Not used (0 read)                                                                                                                                                                                                                                                                                              |     |

Table 3-2 I/O address definition

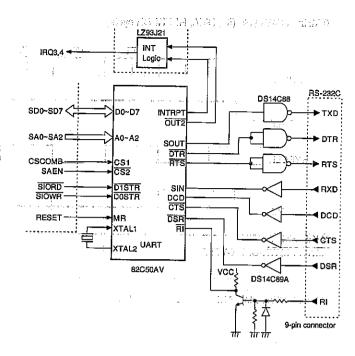

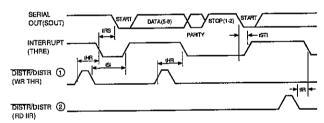

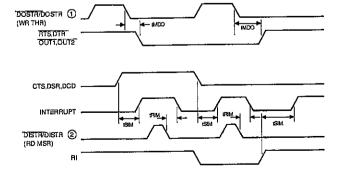

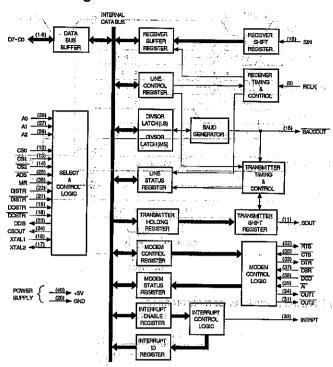

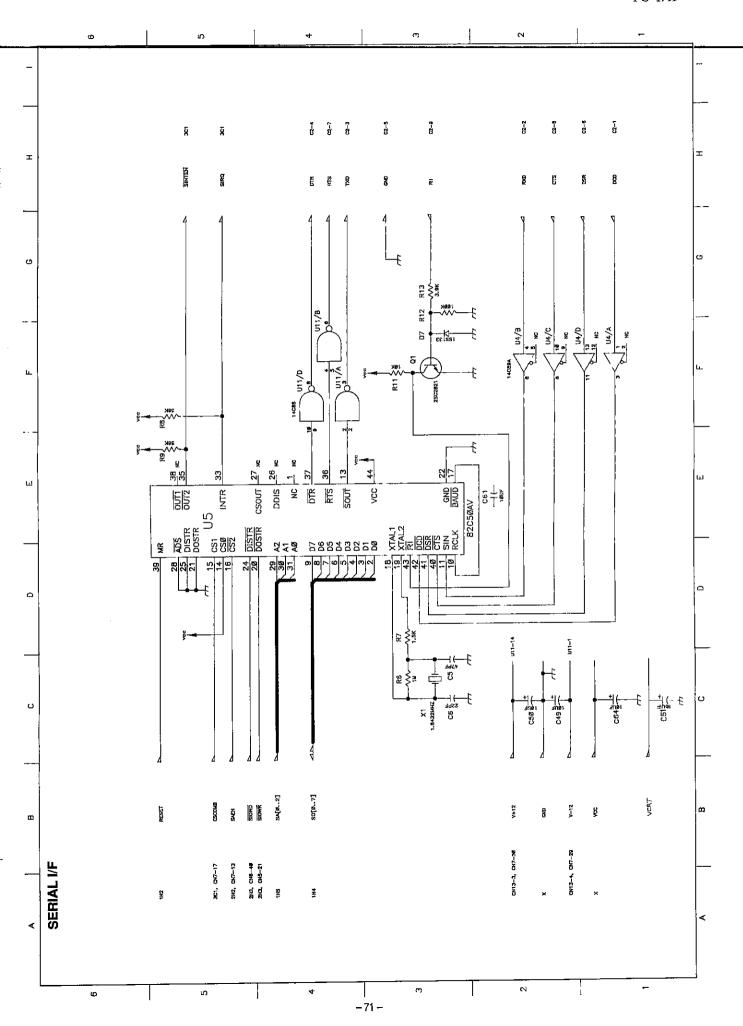

### 3-12. Serial interface

As a standard, the PC-4700 has a serial interface which is assigned at the I/O address 3F8H through 3FFH or 2F8H through 2FFH.

Assignment of the serial interface I/O address to 3FXH or 2FXH is determined by the SCM (LU57832) output signal COM1/\overline{\overline{Z}}. When COM1/\overline{\overline{Z}} is at a low, the serial interface I/O address is assigned to 3FXH. If high, the address is assigned to 2FXH.

1.00 2.00 00 000

Fig. 3-14 Serial interface circuit

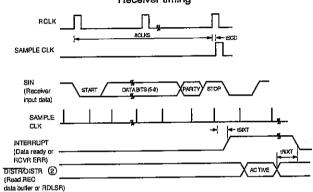

The serial interface circuit consists of transmitter DS14C88, receivers DS14C89A and the UART (INS82C50A). The convert TTL compatible signals sent from the UART to -12V to +12V signals conforming to the EIA standard, and output them via the RS-232 connector. The convert the EIA level reception signal to the TTL level and send it to the UART. The functional configuration of the UART is programmed by software via the data bus.

The UART performs a serial-to-parallel conversion of data characters received from a peripheral device or a MODEM, and a performs a parallel-to-serial conversion of data characters received from the CPU. The CPU can read the complete status of the UART any time during the functional operation. Status information includes the type and condition of the transfer operations performed by the UART, and provides error conditions (parity, overrun, framing, or break interrupt).

The UART includes a programmable baud rate generator. Also the UART has a complete modern control capability and a processor-interrupt system that minimizes the computing time for handling the communications link.

When the CPU assigns one of the address 3F8H through 3FFH or 2F8H throu 2FFH as an I/O address, the HIGH level CSCOMB signal sent from the VG301A (Gate Array) is emitted to the UART. The UART their selects the internal register to be ZORC connected to the data bus according to the state of the DLAB (Divisor Latch Access Bit). The DLAB is bit 7 of the line control register. Table lists the state of registers indicates at each I/O address, and the table lists the bit assignment of each register.

| I/O          | A2    | A1  | A0       | SIORD | SIOWR | DLAB    |                                   |

|--------------|-------|-----|----------|-------|-------|---------|-----------------------------------|

| Address      | . 25. |     | <u> </u> |       |       | F 16 45 |                                   |

| 3F8H or 2F8H | L.    | ,L  | L        | L,    | : H ; | X       | Receive buffer register           |

| 3F8H or 2F8H | L .   | L   | ,L       | Н     | L     | Х       | Transmit holding register         |

| 3F8H or 2F8H | L     | Ļ   | L        | . *   | *     | . 1     | Divisor latch LSB                 |

| 3F9H or 2F9H | Ь     | , L | H        | *     | *     | 1       | Divisor latch LSB                 |

| 3F9H or 2F9H | L     | L   | Нį       | *     | *     | 0       | Interrupt enable register         |

| 3FAH or 2FAH | ᅵᅵ    | Н   | L        | *     | * ,   | Χ       | Interrupt identification register |

| 3FBH or 2FBH | L,    | Н   | H        | *     | *     | X       | Line control register             |

| 3FCH or 2FCH | Н     | L   | L.       | *     | *     | Χ       | Modem control register            |

| 3FDH or 2FDH | Н     | L   | Н        | *     | *     | Х       | Line status register              |

| 3FEH or 2FEH | H     | н   | L.       | _*    | *     | Х       | Modern status register            |

<sup>\*:</sup> SIORD becomes LOW at read operation SIOWR becomes LOW at write operation

X: Not applicable.

| I/O Address    | Bit          | Description                                    |

|----------------|--------------|------------------------------------------------|

| -SF9H-or-2F9H- | <del>0</del> | H: Enable data                                 |

| Interrupt      | 1            | H: Enable TX holding register empty            |

| enable         |              | interrupt                                      |

| register       | 2            | H: Enable receive line status interrupt        |

|                | 3            | H: Enable modem status interrupt               |

|                | 4 – 7        | Always LOW                                     |

| 3FAH or 2FAH   | 0            | H: No interrupt pending                        |

| Interrupt      | 1 .          | Interrupt identification bit 0                 |

| identification | 2            | Interrupt identification bit 1                 |

| register       | 3-7          | Always LOW                                     |

| 3FBH or 2FBH   | 0            | Word length select bit 0                       |

| Line           | 1            | Word length select bit 1                       |

| control        | 2            | Number of stop bit                             |

| register       | 3            | Parity enable                                  |

|                | 4            | Even parity select                             |

|                | 5            | Stuck parity<br>Set break                      |

|                | 6<br>7       | Divisor latch access bit (DLAB)                |

|                |              |                                                |

| 3FCH or 2FCH   |              | Data terminal ready (DTR)                      |

| Modem          | 1            | Request to send (RTS) Out 1                    |

| control        | 2            | Out 2                                          |

| register       | 4            | Loopback                                       |

|                | 5 - 7        | Always LOW                                     |

| 3FDH or 2FDH   |              | Data ready (DR)                                |

| Line           | 1            | Overrun error (OR)                             |

| status         | 2            | Parity error (PE)                              |

| register       | 3            | Framing error (FE)                             |

| '-3            | 4            | Break interrupt (BI)                           |

|                | 5            | Transmit holding register empty (THRE)         |

|                | 6            | TX Shift empty (TSRE)                          |

|                | 7            | Always LOW                                     |

| 3FEH or 2FEH   | 0            | Delta clear to send (DCTS)                     |

| Modem          | 1            | Delta data set ready (DDSR)                    |

| status         | 2            | Trailing edge ring indicator (TERI)            |

| register       | 3            | Delta data carrier detect (DDCD)               |

|                | 4            | Clear to send (CTS)                            |

|                | 5            | Data set ready (DSR)                           |

|                | 6            | Ring indicator (RI) Delta carrier detect (DCD) |

| 1              | 7            | Delta camer detect (DCD)                       |

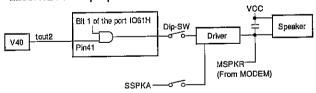

### 3-13. Speaker interface

A small, permanent magnet speaker is used in the sound system. The speaker can be driven from one or two of sources. It also can be driven by the SCM, CE-462M (modem).

- An LZ95H12 output bit

- A timer clock channel, output programmable within the function of the V40 timer. The timer gate can also be controlled by the LZ95H12 PPI output port.

Fig. 3-15 Speaker controll circuit

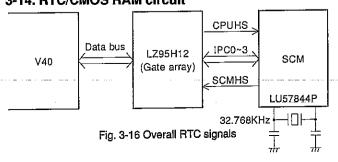

### 3-14. RTC/CMOS RAM circuit

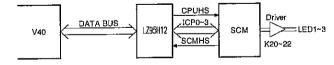

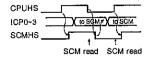

The SCM has a 32.768KHz crystal oscillator for the timer clock besides the program executing oscillator, and divided to cause an interrupt to the SCM itself at the given interval. Timer clock is counted in this interrupt routine and stored in the internal RAM (C-MOS RAM). This value can be read by the V40 via the LZ95H12 by means of handshaking.

For setup data are contained in SCM internal RTC and others, they can be read and written from V40 via LZ95H12 as handshaked with SCM, similar as RTC.

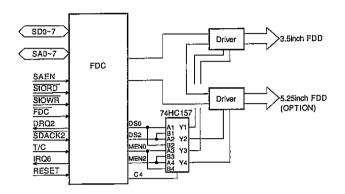

### 3-15. FDD interface circuit

The FDD interface circuit supports two floppy disk units at a maximum. Fig. 3-16 shows the block diagram. A TC8566F floppy disk controller is used to interface the floppy disk units with the CPU.

NOTE: The 74HC157 is used to select between the built-in 3.5 inch FDD and optional 5.25 inch FDD for drive A in the set-up

Fig. 3-16 FDD interface block diagram

### 3-15-1, TC8566F floppy disk controller

The TC8566F floppy disk controller contains a VFO and peripheral logic circuit on a single chip.

Two control registers, main status register, and data register are on the chip. Table 3-3 shows the relation between address line and registers.

| AEN | CS | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Function             |

|-----|----|----|----|----|----|----|----|----|----|----------------------|

| Н   | Χ  | Х  | Х  | Х  | Χ  | Х  | Х  | Х  | X  |                      |

| Х   | Н  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Χ  |                      |

| Х   | Х  | L  | X  | X  | Х  | Х  | Х  | Х  | Х  |                      |

| Х   | Χ  | Х  | L  | X  | Χ  | Х  | Х  | Х  | X  | No selection         |

| Х   | Χ  | Х  | X  | L  | Х  | Х  | Χ  | Х  | Х  |                      |

| X   | Χ  | Х  | X  | Х  | L  | Χ  | Х  | Х  | Х  | ]                    |

| Х   | Х  | Х  | Х  | Х  | Х  | Н  | Χ  | Х  | Х  |                      |

| L   | L  | Н  | Н  | Н  | Н  | L  | L  | L  | L  | Prohibit             |

| L   | L  | Н  | Н  | Н  | Н  | L  | L  | L  | Н  | - TOMBIL             |

| L   | L  | Н  | Н  | Н  | Н  | L  | L  | Н  | L  | Control register-0   |

| L   | L  | Н  | Н  | Н  | Н  | L  | L  | Н  | Н  | Control register-1   |

| L   | L  | Н  | Н  | Н  | Н  | L  | Н  | L  | L  | Main status register |

| L   | L  | Н  | Н  | Н  | Н  | L  | Н  | 1  | Н  | Data register        |

| L   | L  | Н  | Н  | Н  | Н  | L  | Н  | Н  | L  | No selection         |

| L   | L  | Н  | Н  | Н  | Н  | L  | Н  | Н  | Н  | INO SCIECTION        |

Table 3-3

### **3-15-1-1: Control register-0** to be 4 05-04 at a local back left.

This an 8-bit write only register.

|              | <u> </u>                | A Maria and a state                   | <u>, regression Mesjak Nikipak etaken 195</u>        |

|--------------|-------------------------|---------------------------------------|------------------------------------------------------|

| Bit position | Symbol                  | Name                                  | Significance                                         |

| D7           | MEN3                    | Motor enable-3                        | Control bit to control the                           |

| A A PERM     | 10 15 1 1               | The second of the second              | motor in the No. 3 drive                             |

| finy iron    | er i berek<br>Languagia |                                       | unit as an impassion beginning                       |

| D6           | MEN2                    | Motor enable-2                        | Control bit to control the                           |

|              | İ                       |                                       | motor in the No. 2 drive                             |

| <u> </u>     |                         | 5 in -                                | gunit.                                               |

| D5           | MEN1                    | Motor enable-1                        | Control bit to control the                           |

| 3 4 2        |                         |                                       | motor in the No. 1 drive                             |

|              | 0 ,/ 1                  | <u> </u>                              | unit,                                                |

| D4           | MEN0                    | Motor enable-0                        | Control bit to control the                           |

|              |                         |                                       | motor in the No. 0 drive unit.                       |

| D3           | ENID                    | Enable INT &                          |                                                      |

| 53           | CIVID                   | DMA request                           | Used to set INTRQ and DRQ2 into effect. When         |

| 1            | ĺ                       | DIVIN Lednest                         | this bit is at a low, INTRQ                          |

|              |                         | i i                                   | and DRQ2 stay inactive.                              |

| D2:          | FRST                    | Not FDC reset                         | Used to reset the internal                           |

|              |                         |                                       | FDC. When this bit is 0,                             |

|              |                         |                                       | the FDC block is reset.                              |

| D1           | DSB                     | Drive select B                        | Used to select FDC.                                  |

| D0           | DŞA                     | Drive select A                        | The following is selected                            |

|              |                         |                                       | with DSB and DSA.                                    |

|              | ŀ                       |                                       | (0, 0): No. 0 drive unit                             |

|              |                         |                                       | (0, 1): No. 1 drive unit<br>(1, 0): No. 2 drive unit |

| ! !          |                         |                                       | (1, 1): No. 3 drive unit                             |

| 1            |                         |                                       | But, if CDS is low, those                            |

|              |                         | .                                     | bits are not in effect and                           |

|              |                         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | bits are not in effect and                           |

|              |                         | *                                     | the internal FDC select sig-                         |

|              |                         |                                       | nal becomes effective. All                           |

|              |                         |                                       | bits will be cleared when                            |

| L            |                         |                                       | RESET is set high.                                   |

All bits will be cleared when RESET is set high.

Table 3-4

### 3-15-1-2. Control register-1

This an 8-bit write only register.

|                 |        |                      | No. of the control of |

|-----------------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>position | Symbol | Name                 | Significance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D3              | C3     | Control-5            | These bits are open to user. Bit state appears on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D4              | C4     | Contròl-4            | C5 and C4.  If C4 is connected with MIN, for instance, the minifloppy disk can be changed to the standard floppy disk by means of software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D2              | SBM    | Standby mode         | This bit indicates standby mode. Standby mode would not occur when this bit is at 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DO              | FDCTC  | FDC terminal counter | Used to control the FDC terminal count. When data transfer is terminated in the non-DMA mode, the terminal count is sent to the internal FDC block in reference to this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 3

All bits will be cleared when RESET is set high. For data bus, D7, D5, D3, D1, are bit enable signal for D6, D4, D2, and D0, it is possible to change bit independently. For instance, writing 03H changes only FDCTC to 1 without changing the contents of C6, C4, and SBM.

### 3-15-2. Interfacing the FDC register with CPU

Interfacing the FDC register with CPU

The FDC has two registers which can be accessed by the main system processor. The one is main status register and the other is data register. The main status register indicates the FDC status information and can be accessed at any time. The 8-bit data register stores data, command, parameter, and FDD status. Data byte is written in the data register or read from the data register for programming or to obtain the results after command execution. The main status register is read only to facilitate data transfer between the FDC and the processor. The following shows the relation among the main status register, data register, IOR, IOW, and CS.

Condition: A7=A6=A5=A4=A2=1, A3=A1=0, AEN=0

| cs  | A0   | IOR  | IOW . | Function                  |

|-----|------|------|-------|---------------------------|

| Low | Low  | Low  | Low   | Prohibited                |

| Low | Low  | Low  | High  | Main status register read |

| Low | Low  | High | Low   | Prohibited                |

| Low | High | Low  | Low   | Prohibited                |

| Low | High | Low  | High  | Data register read        |

| Low | High | High | Low   | Data register write       |

Table 3-6

Each main status register bit is defined as in Table 3-7.

The main status register bits, RQM and DIO, indicate whether the data register is ready or which direction data are on the data bus.

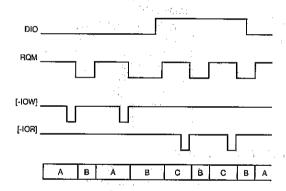

Fig. 3-17 Main status register timing

A (DIO=low, ROM=high):

Data register is enabled to write by the processor.

B (RQM=low)

Data register is not ready.

C (DIO=high, RQM=high)

Data register is read by the processor and a next data byte is already on.

| Bit<br>Position | Symbol | Name               | Significance                                                                                                                                                                                                                                                                                            |

|-----------------|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7              | RQM    | Request for master | Indicates that data are sent<br>to the processor from the<br>data register, or it is ready<br>to receive data from the<br>processor.                                                                                                                                                                    |

| D6              | DIO    | Data input/output  | Indicates data transfer direction when transferring data between the data register and the process or. A high on this line indicates that data are transferred from the data register to the processor. A low on this line indicates that data are transferred from the processor to the data register. |

| D5              | NDM    | Non-DMA mode       | Indicates that the FDC is in the non-DMA mode. This bit can be active only in the execution phase of the non-DMA mode. A low on this line indicates that the execution phase has been completed.                                                                                                        |

| D4              | СВ     | FDC busy           | This bit is set when a read-<br>wirte related command is<br>in execution or during ex-<br>ecution of command phase<br>or result phase.                                                                                                                                                                  |

| D3              | D3B    | FDD3 busy          | Indicates that the NO. 3 drive is in the seek mode.                                                                                                                                                                                                                                                     |

| D2              | D2B    | FDD2 busy          | Indicates that the NO. 2 drive is in the seek mode.                                                                                                                                                                                                                                                     |

| D1              | D1B    | FDD1 busy          | Indicates that the NO. 1 drive is in the seek mode.                                                                                                                                                                                                                                                     |

| D0              | D0B    | FDD0 busy          | Indicates that the NO. 0 drive is in the seek mode.                                                                                                                                                                                                                                                     |

Table 3-7. Main status register

The FDC may execute 15 different commands. Execution takes place with a multiple byte transfer by the processor, and results after command execution is indicates after multiple byte transfer to the processor. For multiple number of bytes are transferred between the FDC and the processor, it may be assumed to constitute the following blocks.

Command phase:

The FDC receives from the processor information required for the given operation.

Execution phase:

The FDC executes the given command.

Result phase:

After completion of the operation, the result status information are sent to the processor.

During execution of command phase and result phase, the processor needs to read the main status register before the byte information is written in the data register or read byte information from the data register. In order to write command and parameter bytes in the FDC, the main status register bit D7 must be high and bit D5 low. For majority of commands requires a multiple bytes, the main status register must be read before transferring bytes to the FDC. Also, the main status register bits D7 and D5 must be high before reading bytes from the data register during execution of the result phase. For the command phase and result phase, the main status register must be read before transferring bytes to the FDC, but may not be required necessarily for the execution phase. When the FDC is in the non-DMA mode, receive of data bytes (when the FDC is reading data from the FDD), INT (INT=1) is caused. If IOR (IOR=0) is issued, it not

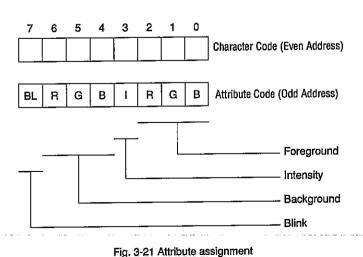

only send data on the data bus, INT may also be reset. However, if the processor may not be fast enough to handle the interrupt (within 13µs in the MFM mode), the main status register is interrogated. The bit D7 (RQM) function as INT. In the same manner, INT may be reset with IOW while write command is in execution.